高速 PCB 的優勢:實現可靠資料傳輸率的先進設計與製造

2 分鐘

- 高速性能必備的先進材料

- 可靠高速 PCB 的成熟設計方法

- 完美高速 PCB 的精密製造

- JLCPCB 在高速 PCB 量產的專業能力

- 常見問題 (FAQ)

那麼,什麼是高速 PCB 設計?它不僅僅是頻率門檻,而是當走線特性對訊號變得不友善時——例如走線阻抗、過孔寄生、材料損耗、訊號耦合等——開始真正影響訊號品質,你再也無法「隨便插上就希望它能跑」,而是必須經過設計。

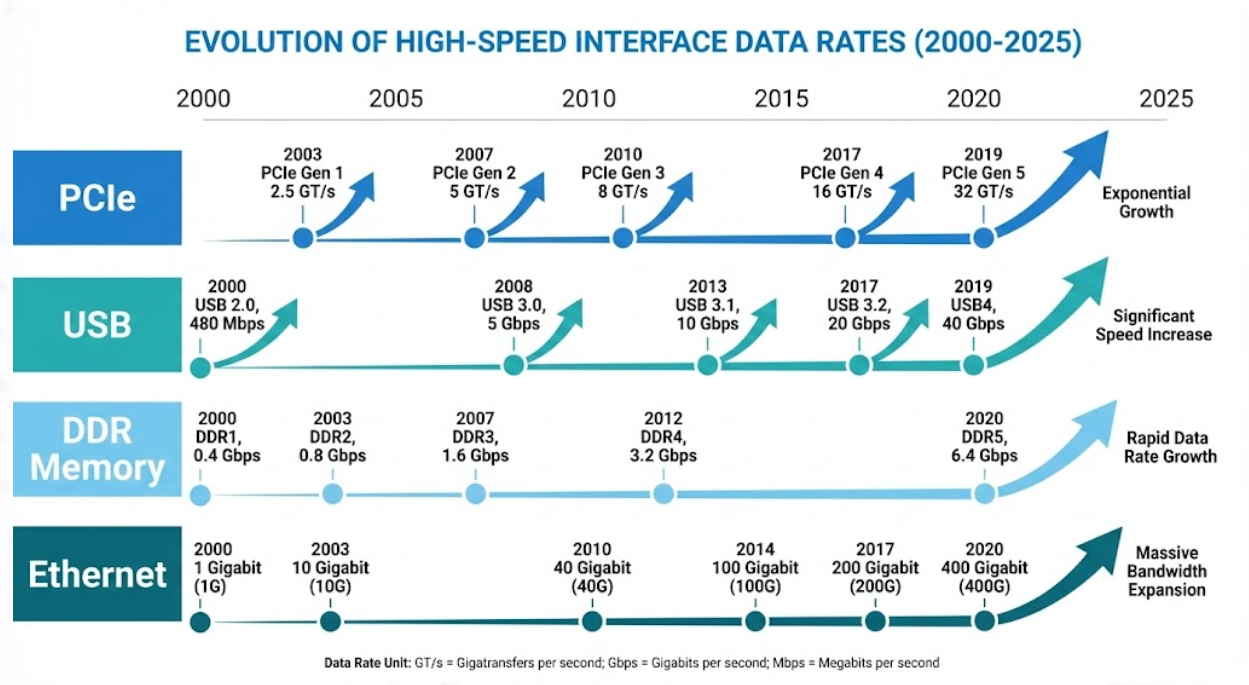

實務上,這通常代表上升時間在奈秒級、每通道的資料速率達到 Gbps,或時脈速度達數百 MHz。然而,現代介面早已遠超這些極限:PCIe Gen5 可達 32 GT/s、USB4 達 40 GB/s、DDR5 達 6.4 GB/s,而 100G/400G 乙太網每通道達 25–56 GB/s。在這樣的速度下,每一密耳的走線、每一個過孔轉換、每一次材料選擇,都是影響系統性能的設計決策。

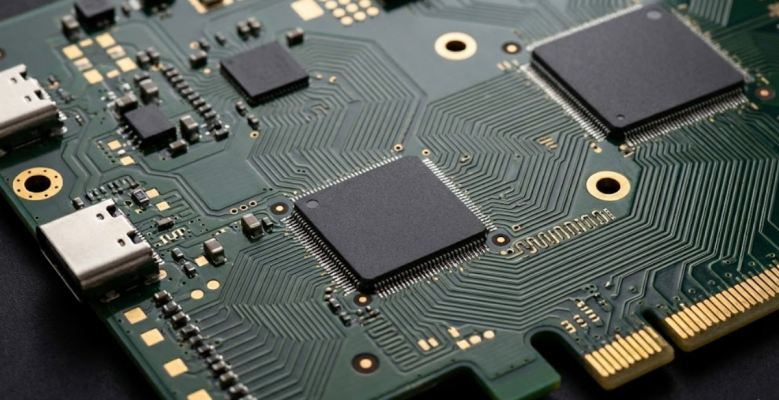

電子工程師已將高速 PCB 設計視為一項專業技能,而非小眾能力。幾乎所有現代 SoC、FPGA 或處理器都至少具備一個高速介面,必須採用適當的 PCB 設計方法。

高頻常見的訊號完整性挑戰

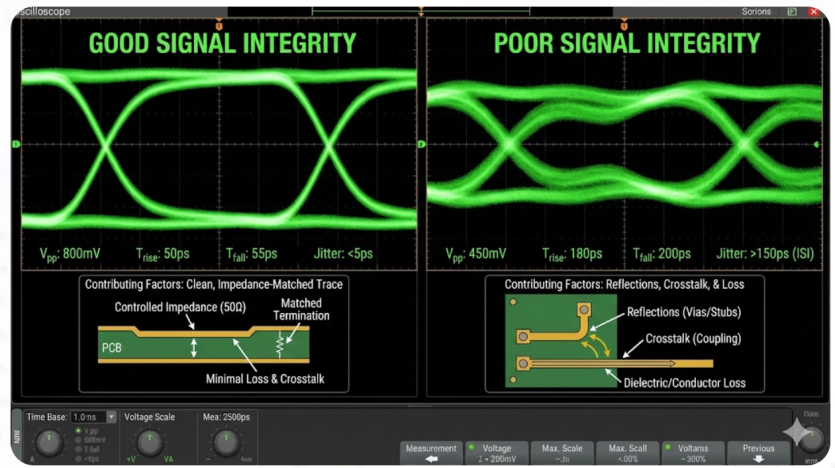

高速數位訊號與射頻訊號面臨相同的物理挑戰,但情境不同。射頻工程師擔心插入損耗與回波損耗,而數位訊號完整性工程師則關注眼圖裕度與位元錯誤率,但底層物理完全相同。

主要挑戰包括:頻率相關損耗(快速數位邊緣的高次諧波衰減更多,使訊號邊緣變圓、眼圖閉合)、過孔、連接器與走線變化處的阻抗不連續造成反射(表現為振鈴與過衝)、相鄰干擾訊號的串音耦合雜訊進入受害走線,以及電源配送網路雜訊透過電源引起的時序變化注入抖動。

隨著資料速率提升,這些效應會疊加。在 5 Gbps 看起來乾淨的訊號,在 25 Gbps 時可能因高頻內容損耗加劇、時序裕度從奈秒縮小到皮秒而完全無法使用。

高速性能必備的先進材料

低損耗介電與高效能基板

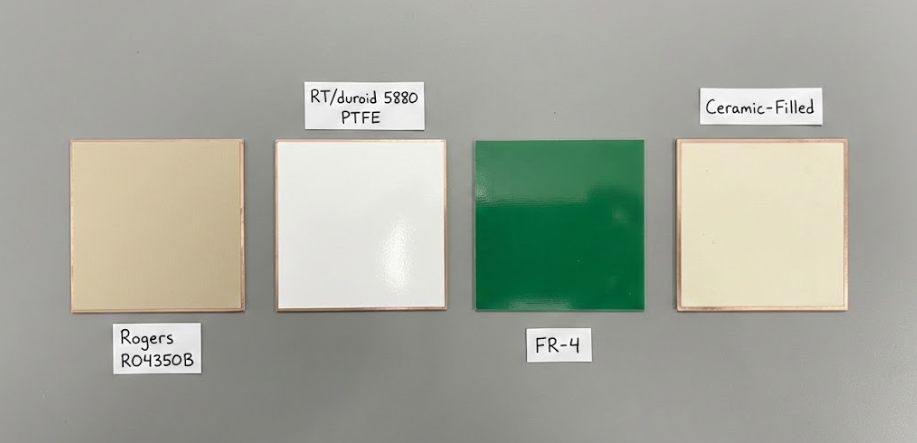

標準 FR-4 已服務產業數十年,但高速 PCB 材料需求已超越其能力。在 10 GHz(25 Gbps NRZ 訊號的相關頻率)時,標準 FR-4 僅介電損耗就約 1 dB/inch,典型走線長度即可耗掉大部分鏈路損耗預算。

高速 PCB 材料業界分級明確。中損耗選項如 Isola FR408HR 與 Panasonic Megtron 4 在成本增加有限下,性能較一般 FR-4 提升,適用於約 10–16 Gbps 的專案。當推進至 25–56 Gbps 時,可考慮 Megtron 6、Isola I-Tera MT40 或 Tachyon 100G 等低損耗材料,其在 10 GHz 的 Df 值可達 0.003–0.005。若要達到 100+ Gbps 的頂級性能,則需接近 PTFE 等級的超低損耗板材。

材料選擇應基於通道損耗預算分析,而非一概而論。某些走線夠短,即使標準 FR-4 也能提供足夠裕度;其他則需高階材料。逐條分析每條關鍵網路。

銅箔粗糙度控制與熱特性

銅箔粗糙度在高頻下對導體損耗影響顯著——與射頻設計師關注的趨膚效應相同。在 25+ Gbps 高速數位應用中,標準銅與低粗糙度反向處理銅的差異可達 0.2–0.4 dB/inch,10 吋以上走線長度累積可觀。

高速基板的熱特性對可靠度也很重要,特別是在高功耗系統。玻璃轉移溫度 (Tg)、分解溫度 (Td) 與熱膨脹係數 (CTE) 必須符合組裝回焊曲線與產品操作溫度範圍。多數高階高速材料在電氣性能外也提供更佳的熱特性。

成本、可靠度與速度的材料權衡

高速 PCB 製造的材料選擇需多方平衡。高階材料降低訊號損耗,但板料成本增加 2–5 倍,若製造商對該材料經驗不足,也可能影響良率。部分超低損耗材料的 Tg 較低或加工難度高於標準 FR-4。

最具成本效益的方法是分析實際鏈路預算,選擇能滿足裕度的最低性能材料;若僅部分層需高階材料,可採用混合疊構。並務必確認板廠對所選材料有量產經驗——不熟悉材料可能導致良率問題,反而抵消選用較便宜材料的節省。

專業提示: 在選材前先用通道損耗模擬(如 Keysight ADS、Ansys HFSS 或免費的 Saturn PCB Toolkit)評估,即可精確得知損耗預算與所需材料等級——無需猜測。

可靠高速 PCB 的成熟設計方法

阻抗控制、差分對走線與疊構

所有高速訊號都必須做成可控阻抗傳輸線。單端訊號通常 50 Ω;差分對則依介面標準為 85、90 或 100 Ω。達到目標阻抗的走線幾何由疊構設計——層厚、介電常數、銅厚——決定。

差分對走線時,+、– 兩線全程間距須保持一致,對內長度差(intra-pair skew)須控制在數 mil 內。對間長度差(inter-pair skew)在並列介面如 DDR5 中亦需考量。

優秀的高速疊構會把所有訊號層緊鄰實心參考平面,並將最重要訊號置於靠近板中心層以獲得最大屏蔽。訊號層與 GND/Power 平面交替,可確保回流路徑完整。

背鑽與串音抑制技術

過孔殘樁(via stub)是未使用的孔段,會產生四分之一波諧振,在頻響造成深凹陷。對標準 62 mil 板厚,殘樁諧振約落在 12 GHz,正好落在 25 Gbps 所需頻帶內。

背鑽以機械方式從板面鑽除未使用的孔銅,需深度控制 ±4 mil 典型值,以完全去除殘樁又不傷及訊號層。高於 10 Gbps 的設計幾乎都值得做背鑽。

串音抑制綜合多項技巧:保持足夠走線間距(至少 3 倍介質高度)、在差分過孔對旁放 GND 參考孔、於相鄰高速通道間插入 GND 走線或銅皮、避免干擾與受害走線長距平行。

設計初期即導入模擬與 DFM

佈線前模擬對高速設計並非可選,而是成功基礎。通道模擬可驗證材料、疊構、走線幾何、過孔、連接器組合能否在目標速率提供足夠訊號品質,且應在走線前完成。

設計階段導入 DFM,可確保模擬結果能夠製造。線寬/間距須符合板廠與銅厚能力;過孔幾何須符合鑽孔深徑比;背鑽深度須留有製程裕度。早期 DFM 審查可避免設計完成才發現製程限制的痛苦循環。

完美高速 PCB 的精密製造

嚴格公差的蝕刻、鑽孔與層間對位

高速 PCB 製造 需一般板子未要求的精度。線寬公差 ±0.5 mil 或更嚴,確保阻抗落在規格內;層間對位 ±2 mil 或更嚴,保持走線與參考平面一致。

鑽孔位置精度影響過孔與焊盤對位,並決定背鑽品質。背鑽需停在距目標層 ±4 mil 內,既去殘樁又不傷訊號層,需具備即時深度監控的 Z 軸控制鑽機。

蝕刻輪廓決定成品走線截面形狀,影響阻抗精度。先進蝕刻製程減少側蝕,產生更矩形輪廓,更接近設計工具計算值。

表面處理與壓合:將訊號劣化降至最低

表面處理影響高速訊號在元件介面的性能。ENIG 為細間距 BGA 提供平整可靠表面,但鎳層磁損在 5 GHz 以上可測;沉銀損耗更低且平整,但保存期短;OSP 成本最低、損耗最小,適合板子製作後短期內組裝。

壓合品質直接影響阻抗控制與介電損耗。精準的樹脂流動控制,可保持訊號層與參考平面間介電厚度一致;樹脂流動不足會留空隙,改變有效介電常數;流動過度則介電變薄,阻抗偏移。

完整測試:TDR 與眼圖分析

TDR(時域反射計)測試阻抗條,驗證 成品阻抗 是否符合設計目標。高速板可依鏈路預算指定 ±7% 或 ±5%。

專用測試通道的眼圖量測,提供最完整的高速 PCB 品質驗證。透過 PRBS 碼型經測試結構傳送並量測接收眼圖,可直接評估所有損耗、反射與耦合對訊號品質的綜合影響,最終證明板子能否支援目標速率。領先的 高速 PCB 設計 服務商已將 TDR 與插損數據列為標準品質文件,讓設計師對板子性能信心滿滿。

JLCPCB 在高速 PCB 量產的專業能力

優質材料夥伴與尖端產線

JLCPCB 與領先基板廠合作,提供從增強 FR-4 到超低損耗材料的全方位選擇,搭配可達多 Gigabit 訊號完整性所需嚴苛公差的精密設備,實現端到端高速 PCB 製造能力。

專為高速設計的 DFM 專家審查

高速設計需要超越一般板子的 DFM 關注。JLCPCB 的 DFM 流程評估疊構可行性、所選材料能否達到目標阻抗、背鑽深度需求等高速專屬因素,提前發現通用 DFM 工具遺漏的問題,避免生產延遲與性能意外。

可擴展製造與經驗證的高良率

從原型驗證到大量生產,JLCPCB 保持 PCB 性能一致。相同的材料規格、製程控制與品質檢驗,在任何規模都適用,讓你驗證過的原型設計,在擴產到數千片時依然表現一致。

常見問題 (FAQ)

什麼算是高速 PCB?

只要訊號互連行為顯著影響訊號品質,即屬高速。實務上,資料速率 >1 Gbps、上升時間 <1 ns,或含 PCIe Gen3+、USB 3.0+、DDR4/5、多 Gigabit 乙太網等介面的板子皆屬之。

何時該從 FR-4 換到高階基板?

當通道模擬顯示 FR-4 損耗佔用過多鏈路預算,導致眼圖無法維持時。粗略而言,>10 Gbps 介面通常受益於增強或低損耗材料,>25 Gbps 幾乎必需。

背鑽對高速設計有多重要?

對 >8–10 Gbps 的通孔過孔非常重要。過孔殘樁諧振會在通道頻響造成深凹陷,嚴重劣化訊號品質。背鑽可消除此諧振,是 25+ Gbps 設計的標準做法。

我應指定多少阻抗公差?

±10% 對大多數 <10 Gbps 高速數位應用已足夠;25+ Gbps 時依鏈路預算指定 ±7% 或 ±5%。更緊公差會提高製造成本,請按實際性能需求訂定。

高速與一般設計能否共存於同一板?

當然可以。多數現代板子同時具備高速介面(PCIe、DDR、乙太網)與一般控制訊號及電源管理。關鍵是僅在需要處採用高速設計技巧:針對高速訊號使用可控阻抗與優質材料,其餘則按常規走線。

持續學習

過孔對高速 PCB 設計的影響

高速訊號需要阻抗匹配。基本上,這表示訊號路徑必須在整個路徑上保持連續阻抗,並與接收器的阻抗相符。這是為了防止訊號反射破壞訊號。用最簡單的話來說,PCB 走線的特性阻抗取決於走線寬度、銅厚、與參考接地平面的距離以及介電常數。在高速設計中,這是一個非常明確的陳述,但導通孔存在幾個問題。導通孔是訊號路徑中的一個 90 度轉彎。導通孔的幾何形狀意味著訊號路徑與 PCB 走線不同。導通孔預設沒有參考平面。 幾何形狀與缺乏參考平面意味著導通孔阻抗通常無法與 PCB 走線匹配。這可能導致訊號反射,進而損害訊號完整性。在影響 PCB 性能的各種因素中,導通孔在高速與高頻電路中對維持訊號完整性與降低損耗扮演關鍵角色。本文深入探討導通孔對這類設計的影響,檢視其對訊號傳輸的效應、所面臨的挑戰,以及如何最佳化其使用。在本文中,我們將探討: 在 GHz 頻率下,RF PCB 佈局中的導通孔轉換需要極其精細的設計。 對於 HDI PCB,正確的導通孔轉換設計與 antipad 尺寸對維持阻抗控制至關重要。 接地平面導通孔間距、接地共面波導設計,以及適當使用縫合導通孔對不同頻段皆不可或缺。 什麼是導通孔及其操作特性? 導通孔是......

深入了解 FPGA:詳盡指南

當我還是年輕的電子工程師時,我對 FPGA 非常好奇,現場可程式化邏輯閘陣列(FPGA)是一類可在製造後由使用者設定的半導體裝置。它們內部擁有海量的邏輯閘,使用者可透過程式設計來模擬晶片行為,而無需實際製造晶片。與傳統微控制器或處理器不同,FPGA 在實現客製化硬體邏輯方面提供了無與倫比的彈性。本文將探討 FPGA 的基本原理、應用、優勢、結構、工作原理以及程式設計基礎。 什麼是 FPGA? FPGA(現場可程式化邏輯閘陣列)是一種可重複程式設計的積體電路(IC),用於執行特定硬體層級的任務。與專為單一應用設計的 ASIC(特殊應用積體電路)不同,FPGA 允許使用者定義並修改邏輯組態,提供高度彈性。FPGA 的主要優勢在於我們可以更改程式邏輯並測試不同晶片的功能,這帶來了極大的靈活性。若能直接在硬體上驗證邏輯而無需實際製造晶片,任何邏輯錯誤都能在硬體層面被排除,從而節省大量時間、精力與成本。 為什麼我們需要 FPGA? 硬體彈性:特殊任務需要客製化的數位電路。 並行處理:高速運算需要同時進行多項計算。 快速原型開發:硬體設計師需要一個平台來測試與驗證,再決定是否投入 ASIC。 低延遲處理:任務......

探索 PCB 設計中的關鍵高頻元件

高頻電路設計驅動了當今許多先進技術,從通訊系統到精密雷達與航太級設備。高頻系統與其他電路在本質上並無不同,物理定律依舊適用,電子學基礎也保持一致。 然而,是什麼讓這些電路能處理如此快速的訊號?關鍵在於專門的元件,各自扮演獨特角色,用以穩定與放大訊號並將失真降至最低。HF 設計面臨獨特的挑戰與目標,操作時需特別留意。我們常將元件分為主動或被動,這種分類在射頻領域同樣適用。以下為高頻電路設計中可識別的元件參考指南。 高頻電容器: 從基礎電路元件課程可知,電容器基本上是一個小型儲能單元,會阻擋直流並讓交流訊號通過。理想上它對所有交流訊號都應表現一致,但實際並非如此;其功能會隨施加的交流頻率而改變。以下為表示電容器真實電性行為的模型。 「C」對應埋藏在眾多寄生元件中的理想電容,包含極板間的非無限電阻(RD)、串聯電阻(RS)、串聯電感(LS),以及 PCB 焊盤與接地平面間的並聯電容(CP)。 高頻電感器: 電感器則具有與電容相反的特性。基礎上,它是由銅線繞成的線圈,依法拉第電磁感應定律運作,以磁場形式儲能。它阻擋交流訊號並讓直流輕易通過,可說是抗拒訊號變化。電感提供的阻抗會隨交流訊號頻率升高而穩定增加。......

如何解決高頻 PCB 設計中的 EMI/EMC 與訊號完整性問題

高頻 PCB 設計充滿挑戰,其中電磁干擾(EMI)與訊號完整性(SI)問題最為關鍵。這些問題會降低電路效能、影響可靠度,並導致法規測試失敗。為了解決它們,必須在整個設計流程中仔細規劃與執行。以下為克服這些挑戰的策略。 對於訊號方向複雜的網路,拓撲結構對單向、雙向及不同訊號位準的影響各異,很難判斷哪種拓撲對訊號品質最佳。必須預先進行模擬,工程師需深入了解電路原理、訊號類型,甚至佈線難度,才能選出合適的拓撲。想了解更多 PCB 知識,請參閱我們的 PCB 製造終極指南。 優化 PCB 佈局 以確保訊號完整性的技巧: 佈局是確保訊號完整性的關鍵因素。針對 高頻設計,請注意: 走線長度: 盡量縮短訊號走線,以減少傳播延遲與反射。 阻抗控制: 使用控制阻抗走線,使走線阻抗與源端及負載匹配,尤其對高速訊號更重要。 過孔放置: 在高速訊號路徑中減少過孔使用,因過孔會造成阻抗不連續與反射。 差分對走線: 高速訊號使用緊密耦合的差分對,可降低串擾並維持訊號完整性。 高頻 PCB 佈局設計中如何進行阻抗匹配? 阻抗匹配是高速 PCB 設計的關鍵因素之一。阻抗與走線佈局直接相關,例如走線位於表層(微帶線)或內層(帶狀線......

眼圖在高速 PCB 設計中的角色

在高速 PCB 設計中,訊號完整性至關重要。隨著數位裝置的頻率不斷提高,我們必須確保高速 PCB 上各元件之間的可靠通訊。評估高速設計訊號完整性最有效的工具之一便是眼圖。它可用來評估通道雜訊、色散與符號間干擾對基頻脈衝傳輸系統效能的綜合影響。 眼圖以視覺化方式呈現數位訊號的效能,讓工程師能夠評估雜訊、抖動與時序錯誤等因素。從數學角度來看,眼圖是訊號機率密度函數(PDF)的可視化結果。眼圖中「眼睛」睜得越開,代表訊號失真越小。本文將探討眼圖在高速 PCB 設計中的角色、其重要性,以及如何藉由眼圖改善訊號完整性。 訊號的符號間干擾 符號間干擾(ISI)是指連續訊號因訊號完整性問題而互相干擾的現象。這些訊號可能在頻域或時域上無法區分,兩者無法同時成立,因而產生 ISI(由其他元件引起的非預期雜訊)。此外,我們現已具備在時域零交叉點取樣等技術,可減輕 ISI 的影響。 理想上,我們希望訊號零失真、零抖動、零脈衝擴散與零振幅雜訊,也就是輸出訊號與輸入訊號完全一致。能夠觀察到這一點,正是眼圖成為訊號完整性核心工具的原因。 眼圖的關鍵組成 眼圖是透過在不同時間點重複取樣數位訊號所繪製的圖形。當訊號軌跡疊加在示波......

打通垂直維度:PCB Via 技術選型與高速信號優化指南

隨著訊號上升時間步入皮秒級,印製電路板(PCB)的設計方法正經歷一場轉型。傳統的平面拓樸結構正逐漸被針對垂直互連進行最佳化的方案所取代。在高速訊號傳輸領域,即使是電路板內最微小的孔徑,也可能成為引發訊號反射與損耗的主要來源。究其原因,在於PCB過孔會引入阻抗不連續性。因此,在設計複雜系統時,徹底瞭解各類過孔的物理限制及其固有的電氣特性,是確保系統可靠性的關鍵第一步。 一、 基礎互連:Through Hole Via PCB 限制與優化 印刷電路板中的貫穿孔through hole via PCB是較常見的連接方式,其貫穿整個電路板。貫穿孔的製造成本相對較低,但在高頻領域卻會遇到很多挑戰。 1. 寄生參數的威脅 過孔本質上是一個微型的電容與電感組合。對於高速訊號,過孔的寄生電容會增加信號的上升時間,而寄生電感則會增加路徑阻抗。其寄生電容量可由下式估算: (T:板厚,D1:過孔焊盤直徑,D2:反焊盤直徑) 2. Stub效應 設計多層板時(信號從第一層傳輸到第三層),貫穿孔在第三層以下的部分就會形成開路的傳輸線。在特定頻率下,這可能會引起諧振,嚴重破壞信號的完整性。因此在設計速率超過20Gbps的系統......