透過精密製程實現高頻 PCB 的可靠訊號性能

1 分鐘

- 選擇材料,實現卓越高頻性能

- 高頻 PCB 的必備設計技巧

- 高頻 PCB 的專家級製程

- JLCPCB 在高頻 PCB 交付上的成熟能力

- 常見問題(FAQ)

近期,電子產業持續推高頻率,使得原本單純的 PCB 變成必須嚴肅對待的射頻元件。當前的高頻PCB 設計,其運作速度在十年前簡直難以想像。5G 毫米波基地台在 24–40 GHz 頻段運作,車用雷達晶片工作在 77 GHz,Wi-Fi 7 突破 6 GHz,就連所謂的數位高速序列連接如 PCIe Gen5 與 USB4,也將訊號推進到數 GHz 領域。

在這些 GHz 頻率下,PCB 基材不再只是被動背景。板內任何元素——介電材料、銅箔粗糙度、導通孔幾何、走線尺寸,甚至表面處理——都會在訊號路徑中造成可量化的損耗。若在高頻PCB 設計時忽略這些效懿,將導致訊噪比劣化、傳輸距離縮短、位元錯誤率上升,甚至面臨法規認證陷阱。

優質高頻 PCB 的需求從未如此迫切,容錯空間也從未如此狹窄。要做對,必須選對材料、做好設計,再把細節交給製造專家。

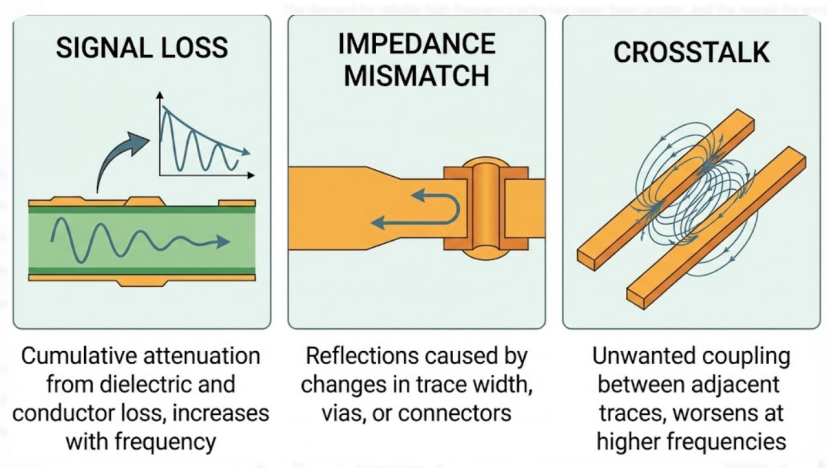

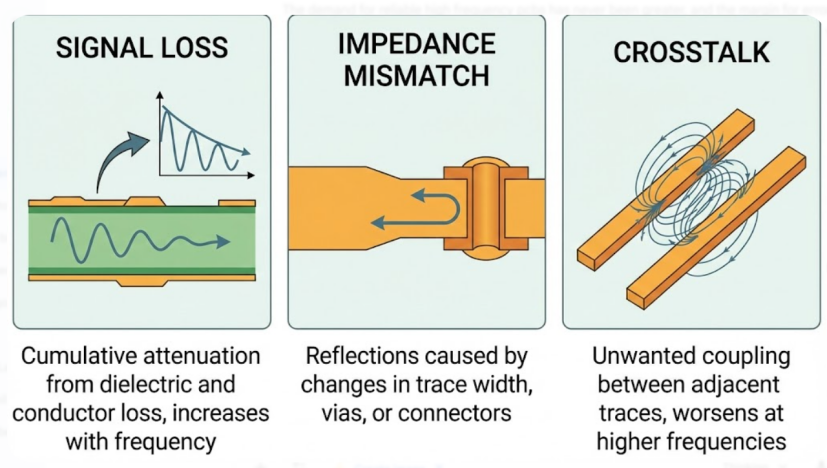

訊號損耗、阻抗不匹配與串擾等挑戰

高頻PCB 設計面臨三大首要挑戰。訊號損耗(插入損耗)是訊號能量在板內傳輸時的累積衰減,來源有二:介電損耗(基材吸收能量)與導體損耗(銅箔因趨膚效應與表面粗糙度而耗散熱能)。兩者皆隨頻率升高而加劇,因此材料選擇至關重要。

阻抗不匹配發生在傳輸線特性阻抗沿路徑變化時:可能因走線寬度變化、經導通孔換層、連接器介面或基材特性改變所致。任何不匹配都會產生反射,奪走傳輸訊號能量,並可能形成駐波,扭曲頻率響應。

串擾:相鄰訊號走線間的無意耦合,隨頻率升高而愈發棘手,因耦合係數隨頻率增加。在 1 GHz 看似足夠的走線間距,到了 10 GHz 可能產生無法接受的串擾,需要更大間距或屏蔽結構。

選擇材料,實現卓越高頻性能

低損耗板材:Rogers、Teflon 與混合方案

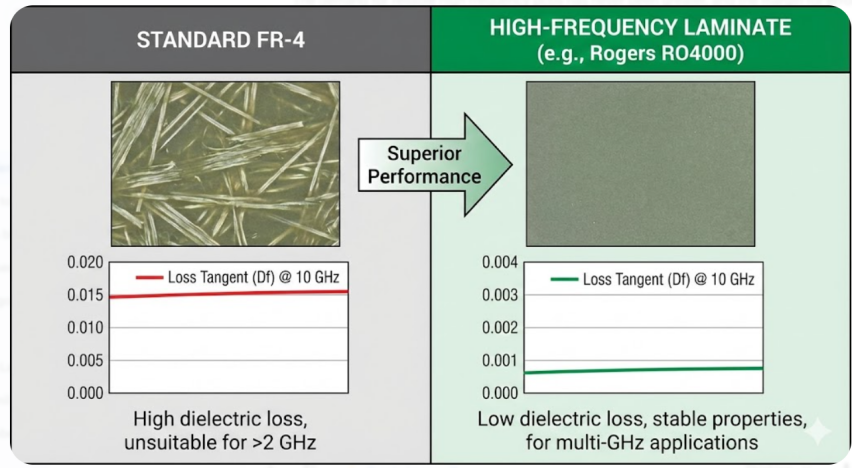

標準 FR-4 板材雖足以應付數百 MHz 以下的數位設計,但在更高頻率下損耗急劇增加。其在 10 GHz 的損耗因子(Df)達 0.020 或更高,使多數 1–2 GHz 以上的高頻 PCB 應用望而卻步。

高頻材料市場提供多種替代方案。Rogers 公司的 RO4000 系列是 FR-4 的經濟升級版,Df 約 0.004,介電特性在寬頻範圍內穩定。更嚴苛應用可選 Rogers RO3000 系列或 PTFE 基材(俗稱鐵氟龍板),Df 低於 0.002,設計可延伸至毫米波頻段。

混合疊構將關鍵訊號層採用高頻板材,非關鍵層使用標準 FR-4,兼顧成本與性能:RF 訊號層享有高階材料,電源與低速控制層則用經濟板材,整體成本降低,關鍵性能不受影響。

關鍵特性:介電常數、損耗角正切與熱穩定性

高頻 PCB 材料選擇由三項特性主導。介電常數(Dk 或 Er)決定走線電氣長度與傳輸線特性阻抗。較低 Dk 可減少走線耦合並實現更緊密的阻抗控制;Dk 穩定性同樣重要,若 Dk 隨溫度或頻率漂移,阻抗控制將不可預測。

損耗角正切(Df)直接告訴你介電損耗有多大。FR4 在 10 GHz 的 Df 約 0.020,而 Rogers 4350B 約 0.0037,單位長度損耗降低約 5 倍,且隨走線長度倍增。

熱穩定性同樣關鍵,因多數高頻系統需在寬溫範圍運作。若材料 Dk 隨溫度劇變,插入損耗與阻抗將隨之改變,導致高低溫性能崩潰。

專業提示:別只看規格書 1 MHz 數據。請向板材商索取你實際工作頻率下的 Dk 與 Df;1 MHz 與 10 GHz 差異巨大,且規格書往往比實際樂觀。

在材料選擇中平衡成本與性能

坦白說,高頻板材面積單價是 FR-4 的 5–20 倍。但你必須選擇符合性能需求的材料,否則只是浪費錢。

若板子速度不超過 3 GHz,可選升級版 FR4——Isola FR408HR、Panasonic Megtron 6 等,價格遠低於 PTFE 材料。3–15 GHz 區間,Rogers RO4000 系列常是性能與易製程的平衡點。超過 15 GHz,即使成本更高、製程更難,也必須使用 PTFE 或陶瓷填充材料。

訣竅在於混合疊構:只在需要的高頻層使用昂貴材料,其餘用普通 FR4,可節省 40–60% 材料成本,同時保留 RF 性能。

高頻 PCB 的必備設計技巧

阻抗控制走線與疊構規劃

每條高頻訊號走線都必須設計成阻抗受控的傳輸線,即指定走線寬度、銅厚、介電厚度與介電常數,以達到目標特性阻抗(單端 RF 通常 50 Ω,高速差分 100 Ω)。

高頻 PCB 疊構設計先找出板上高速訊號,確保每層高速訊號緊鄰完整參考平面,介電厚度固定阻抗,容差需控制在 ±10% 以內,否則全盤皆輸。

切勿在鄰近分割平面或高密度走線層跑高速線。參考平面必須在走線正下方/上方提供無阻礙的回歸路徑,任何不連續都會迫使回歸電流繞行,增加迴路面積並輻射。

導通孔管理與接地平面策略

導通孔是高頻路徑上阻抗突變的最大元兇。孔柱是寄生電感,反焊盤是寄生電容。超過 5 GHz 時,務必縮短孔柱、背鑽或採用盲孔。訊號孔周圍打接地孔是救命稻草:上下平面用接地孔環繞,形成類同軸屏蔽,保持訊號換層時阻抗恆定。

接地平面完整性至上:再小的縫隙、切口或開槽,在高頻走線旁都會變成假天線輻射。若非得跨越切口,於跨越處緊鄰放置縫合電容或接地孔,為回歸電流提供橋樑。

最小化反射並確保訊號完整性

反射出現在阻抗變化處:走線寬度、經孔換層、連接器焊墊、元件焊盤等。源端到負載端阻抗必須恆定,才能將反射降至最低。需改變走線寬度時(如連接器焊盤),使用漸變過渡;換層處務必加接地孔與縫合。

為連接器設計共面波導或接地共面等接地結構,保持板與連接器間阻抗順暢。超過 5 GHz 時,務必使用 2D 截面阻抗工具(布局前模擬)與 3D EM 模擬(孔過渡與連接器),這些模擬能揭露線路圖找不到的缺陷,且在模擬中除錯遠比打樣後翻修便宜。

高頻 PCB 的專家級製程

細線路精密鑽孔、電鍍與蝕刻

高頻PCB 製造必須嚴格控制製程公差,遠非普通板可比。舉例:走線寬度公差需維持 ±0.5 mil,才能讓阻抗落在規格內,這需要精準蝕刻,化學藥水、溫度與輸送速度皆窄帶控制。

鑽孔精度同樣關鍵,孔位必須精準,背鑽深度才能正確。背鑽用於去除未使用的孔柱,深度精度需在 4 mil 內,才能徹底消除孔柱,又不鑽穿受保護的訊號層。

表面銅與孔內電鍍的均勻度,會影響阻抗控制與插入損耗。電鍍不平整會造成局部阻抗突變,表面粗糙度也會增加不必要的導體損耗。

層間對位與表面處理的高精度公差

高頻板層間對位必須極其精準,任何參考平面位移都會改變上方訊號線的有效阻抗。高頻設計需要 2 mil 或更好的對位公差。

表面處理也影響高頻性能。ENIG 提供極平整表面,利於微小 RF 焊墊,但鎳層在極高頻會增加磁性損耗。高頻浸銀幾乎無額外損耗,OSP 損耗最低但保存期短,需在 RF 性能與儲存/組裝條件間權衡。

阻抗與插入損耗驗證的先進測試

所有高頻板皆須透過時域反射計(TDR)測試面板內嵌測試 coupon,確認實際阻抗符合設計值,公差可達 ±10% 或更嚴苛的 ±5%。

關鍵 RF 設計還需量測測試結構的插入損耗,驗證材料組合、銅箔粗糙度與製程步驟是否達到目標訊號性能。這些量測提供模擬無法取代的真實數據。優質高頻 PCB 廠商會隨出貨提供這些測試資料。

JLCPCB 在高頻 PCB 交付上的成熟能力

優質材料與尖端設備

JLCPCB 與 Rogers 等一流板材商合作,能以合理價格取得多款高頻材料,再搭配高精度設備,滿足高頻設計的嚴苛公差,不論快速打樣或大量生產皆能勝任。

高頻設計的專業 DFM 支援

對於高頻新手,早期 DFM 合作極具價值。JLCPCB 工程團隊會預審你的疊構、材料與阻抗需求,指出潛在問題並提供優化建議,讓你在大批量生產前就能修正,省下可觀成本。

從原型到量產的可靠交付

不論 5 片 5G 天線原型,或 5000 片雷達模組量產,JLCPCB 在各批量皆維持一致的高頻性能。所有批量皆採用相同材料規格與品質檢驗,確保原型驗證的設計,在量產時表現如一。

常見問題(FAQ)

什麼是「高頻 PCB」?

高頻 PCB 專為約 1 GHz 以上訊號設計,採用特殊低損耗板材、阻抗受控傳輸線與精密製程,以最小化訊號劣化。確切頻率門檻視應用性能需求而定。

FR-4 能用於高頻嗎?

標準 FR-4 一般僅適用 1–2 GHz 以下非關鍵應用。更高頻率下,其高介電損耗會迅速劣化訊號品質。增強型 FR-4 可延伸至 3–5 GHz。超過 5 GHz 通常需 Rogers 或 PTFE 等高頻板材。

高頻 PCB 製造貴多少?

高頻板通常比同複雜度標準 FR-4 板貴 2–5 倍,主因是高端板材。混合疊構(高頻層與標準材料混用)可將溢價降低 40–60%,同時在關鍵層維持 RF 性能。

高頻 PCB 性能最關鍵的因素?

材料選擇(特別是損耗角正切)對訊號性能影響最大。然而,高端板材若製程公差差,反而不如中端板材精密加工。材料與製程品質皆需卓越,才能達到最佳結果。

我的設計需要背鑽嗎?

約 5 GHz 以上,通孔孔柱會造成顯著阻抗不連續與諧振,此時背鑽重要。更低頻率,或使用盲埋孔(本身無孔柱)設計,則不需背鑽。

持續學習

在 PCB 上設計天線:從初學者到進階的完整指南

在無線連接普及的今日,體積小、價格親民且可靠的天線需求前所未見。天線是電磁波原理的實體實踐,能為各種無線應用收發訊號。儘管相關理論與實驗研究眾多,實際商品化並廣泛採用的設計卻寥寥無幾。 在各種選擇中,印刷電路板(PCB)天線已成為現代裝置的實用方案。將天線直接嵌入電路板,可縮小系統尺寸、降低成本,並省去外部天線模組。這種整合特性使 PCB 天線特別適用於 Wi-Fi 系統、IoT 與 BLE 模組及穿戴式裝置等小型電子產品。本指南將介紹PCB 天線的基礎知識、各種類型、設計考量、最佳實踐,以及進階主題,助您提升天線設計技能。 認識 PCB 天線 PCB 天線是在電路板上形成的金屬走線,用於收發電磁訊號,並設計成在特定頻率或頻段諧振,使裝置得以無線通訊。 PCB 天線的主要優點: 低成本(無需額外製程,僅需 PCB 蝕刻) 體積小且易整合 高可靠性(無活動或可拆零件) 可依應用需求客製 然而,PCB 天線對佈局、接地層與零件擺放相當敏感,需謹慎設計。 PCB 天線的類型 1)倒 F 天線(IFA) 最受歡迎的小型天線之一,彎折結構可節省空間,適用於單頻段,常見於藍牙、Wi-Fi 與行動裝置。體積小、......

射頻 PCB 佈局與製造的設計準則

射頻 PCB 的運作基於一些基本規則,需要事先具備數位與類比設計電路的知識。由於頻率範圍落在 GHz 等級,無法直接與類比或數位電路相比。這樣的頻率範圍讓 PCB 變得截然不同,我們幾乎得重新檢視所有環節: 阻抗不匹配 走線長度 接地 屏蔽 若未妥善處理,可能導致整個系統失效;即使僅部分忽略需求,也會造成性能下降、訊號損失、EMI(電磁干擾)以及功耗增加。我們將探討可用材料、微波 RF PCB 的走線佈線方式,最重要的是訊號完整性與阻抗規則。為避免訊號劣化與區塊間串音,必須謹慎布局。開始 RF 布局前,請先考量以下參數: 7 項 RF PCB 布局關鍵考量 1. 材料選擇 RF PCB 需要穩定的基板。何謂穩定?即穩定的介電常數(Dk)與較低的損耗正切(Df)。常見 RF 材料有 Rogers RO4000、RO3000、Taconic RF 層壓板與 PTFE。較低的介電常數可縮短傳播延遲;較低的損耗正切則能減少能量損失。 2. 控制阻抗 走線可採用微帶線、帶狀線或共面波導結構,詳見後述。此外,必須保持走線寬度與參考接地平面高度一致,以設定特性阻抗(通常為 50 Ω 或 75 Ω)。若線路與網路......

六層 PCB 疊構與堆疊指南

印刷電路板(PCB)是現代電子產品的骨幹,提供連接與支撐各種電子元件所需的基礎架構。隨著電子裝置日益複雜且體積縮小,對多層 PCB 的需求也隨之增加。其中, 6 層 PCB 是許多應用中的熱門選擇。本文將深入探討 6 層 PCB 疊構的細節、其應用、最佳配置,以及挑選最佳製造商的指引。 為何使用 6 層 PCB? 提升功能性: 6 層 PCB 的主要優勢在於能夠容納更複雜的電路。額外的層數讓設計師擁有更多佈線路徑,可實現更高的元件密度與更佳效能,對於空間有限卻需精巧設計的現代裝置至關重要。 改善訊號完整性: 高速電路特別容易受到訊號完整性問題的影響,例如串音與電磁干擾(EMI)。6 層 PCB 提供額外層數作為專屬接地與電源平面,有助於提供穩定的參考平面並降低雜訊,從而維持訊號完整性。 強化電源分配: 6 層 PCB 的額外層數可實現更優異的電源分配。對於具有多種電壓位準與高電流需求的電路尤其重要,有助於降低壓降並確保所有元件獲得穩定的電力供應。 更佳的散熱效果: 散熱管理是 PCB 設計的關鍵環節。6 層 PCB 的額外層數可提供更大表面積與更多熱傳導路徑,有助於散熱,從而提升整體熱效能。 6 ......

過孔對高速 PCB 設計的影響

高速訊號需要阻抗匹配。基本上,這表示訊號路徑必須在整個路徑上保持連續阻抗,並與接收器的阻抗相符。這是為了防止訊號反射破壞訊號。用最簡單的話來說,PCB 走線的特性阻抗取決於走線寬度、銅厚、與參考接地平面的距離以及介電常數。在高速設計中,這是一個非常明確的陳述,但導通孔存在幾個問題。導通孔是訊號路徑中的一個 90 度轉彎。導通孔的幾何形狀意味著訊號路徑與 PCB 走線不同。導通孔預設沒有參考平面。 幾何形狀與缺乏參考平面意味著導通孔阻抗通常無法與 PCB 走線匹配。這可能導致訊號反射,進而損害訊號完整性。在影響 PCB 性能的各種因素中,導通孔在高速與高頻電路中對維持訊號完整性與降低損耗扮演關鍵角色。本文深入探討導通孔對這類設計的影響,檢視其對訊號傳輸的效應、所面臨的挑戰,以及如何最佳化其使用。在本文中,我們將探討: 在 GHz 頻率下,RF PCB 佈局中的導通孔轉換需要極其精細的設計。 對於 HDI PCB,正確的導通孔轉換設計與 antipad 尺寸對維持阻抗控制至關重要。 接地平面導通孔間距、接地共面波導設計,以及適當使用縫合導通孔對不同頻段皆不可或缺。 什麼是導通孔及其操作特性? 導通孔是......

深入了解 FPGA:詳盡指南

當我還是年輕的電子工程師時,我對 FPGA 非常好奇,現場可程式化邏輯閘陣列(FPGA)是一類可在製造後由使用者設定的半導體裝置。它們內部擁有海量的邏輯閘,使用者可透過程式設計來模擬晶片行為,而無需實際製造晶片。與傳統微控制器或處理器不同,FPGA 在實現客製化硬體邏輯方面提供了無與倫比的彈性。本文將探討 FPGA 的基本原理、應用、優勢、結構、工作原理以及程式設計基礎。 什麼是 FPGA? FPGA(現場可程式化邏輯閘陣列)是一種可重複程式設計的積體電路(IC),用於執行特定硬體層級的任務。與專為單一應用設計的 ASIC(特殊應用積體電路)不同,FPGA 允許使用者定義並修改邏輯組態,提供高度彈性。FPGA 的主要優勢在於我們可以更改程式邏輯並測試不同晶片的功能,這帶來了極大的靈活性。若能直接在硬體上驗證邏輯而無需實際製造晶片,任何邏輯錯誤都能在硬體層面被排除,從而節省大量時間、精力與成本。 為什麼我們需要 FPGA? 硬體彈性:特殊任務需要客製化的數位電路。 並行處理:高速運算需要同時進行多項計算。 快速原型開發:硬體設計師需要一個平台來測試與驗證,再決定是否投入 ASIC。 低延遲處理:任務......

探索 PCB 設計中的關鍵高頻元件

高頻電路設計驅動了當今許多先進技術,從通訊系統到精密雷達與航太級設備。高頻系統與其他電路在本質上並無不同,物理定律依舊適用,電子學基礎也保持一致。 然而,是什麼讓這些電路能處理如此快速的訊號?關鍵在於專門的元件,各自扮演獨特角色,用以穩定與放大訊號並將失真降至最低。HF 設計面臨獨特的挑戰與目標,操作時需特別留意。我們常將元件分為主動或被動,這種分類在射頻領域同樣適用。以下為高頻電路設計中可識別的元件參考指南。 高頻電容器: 從基礎電路元件課程可知,電容器基本上是一個小型儲能單元,會阻擋直流並讓交流訊號通過。理想上它對所有交流訊號都應表現一致,但實際並非如此;其功能會隨施加的交流頻率而改變。以下為表示電容器真實電性行為的模型。 「C」對應埋藏在眾多寄生元件中的理想電容,包含極板間的非無限電阻(RD)、串聯電阻(RS)、串聯電感(LS),以及 PCB 焊盤與接地平面間的並聯電容(CP)。 高頻電感器: 電感器則具有與電容相反的特性。基礎上,它是由銅線繞成的線圈,依法拉第電磁感應定律運作,以磁場形式儲能。它阻擋交流訊號並讓直流輕易通過,可說是抗拒訊號變化。電感提供的阻抗會隨交流訊號頻率升高而穩定增加。......