PCB 的 EMI 屏蔽:專業製造中實現卓越電磁相容性的先進技術與材料

1 分鐘

- PCB 上的 EMI 屏蔽原理

- 關鍵 EMI 屏蔽材料及其應用

- 在 PCB 設計中落實有效 EMI 屏蔽

- 專業製程打造可靠 EMI 屏蔽

- 常見問題 (FAQ)

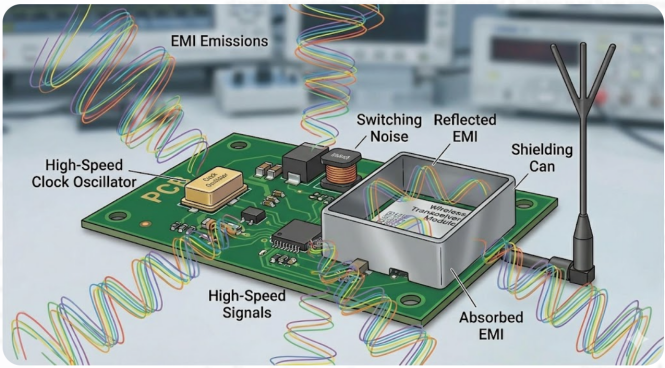

簡單來說,EMI 屏蔽就是將任何導電或磁性材料包圍起來,確保電場與磁場不會在 PCB 的特定區域進出。想像你在脆弱電路外蓋了一個法拉第籠,只是你要保護的不是自己,而是隔壁電路,避免你那吵雜的切換穩壓器干擾它(反之亦然)。現代電子產品已成為 EMI 的夢魘:GHz 等級的時脈、MHz 的切換穩壓器,以及無線電遍布整片 PCB,導致板內與周圍的電磁共振極度混亂。

若未做好 EMI 屏蔽,產品可能無法通過法規測試(FCC、CE、CISPR)、產生自干擾,甚至影響周邊設備。風險極高:缺少 EMC 測試可能讓上市延遲數週或數月,你只能手忙腳亂地加蓋屏蔽罩與濾波器,作為最後一刻的急救,代價永遠比一開始就做對更高、更費工。

PCB 上常見的電磁干擾源

首先,得先找出 EMI 的真正源頭才能馴服它。高速時脈及其諧波、切換電源內的電感與變壓器(同時傳導與輻射雜訊)、USB 3.0、PCIe、HDMI 等資料鏈路發出的寬頻雜訊、刻意發射的射頻天線與振盪器,以及任何快速上升緣的元件,都會在鄰近走線與纜線上激發小電磁場,這些都是 PCB 上的慣犯。

有時問題零件本身就很吵,但即使最普通的元件,只要佈局鬆散也會變成 EMI 嫌疑犯。舉個 LED 驅動器為例:若切換速度過快且電流迴路面積亂七八糟,其輻射量足以讓你無法通過 Class B 輻射測試。

PCB 上的 EMI 屏蔽原理

反射、吸收與接地的協同作用

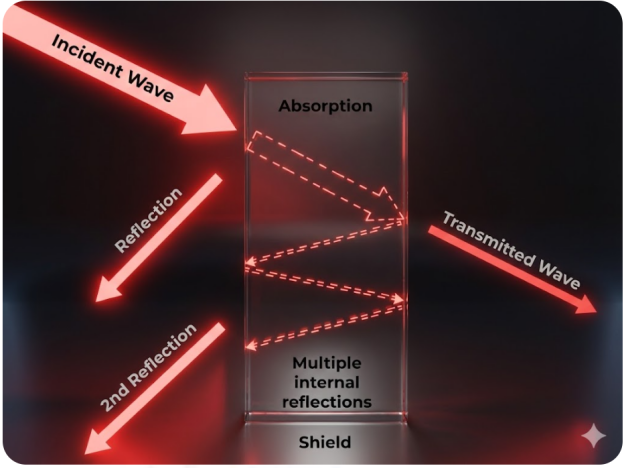

那麼屏蔽罩到底怎麼擋雜訊?關鍵在三大機制協同。低頻時主要靠反射:波碰到導電表面,自由空間與金屬的阻抗差異會讓大部分能量反彈;銅或鋁都是絕佳反射體。

頻率越高,吸收越重要:波進入屏蔽層後因電阻損耗轉為熱。吸收量取決於材料導磁率、導電率與厚度;更厚或高導磁材料(如 mu-metal)效果更好。最後,接地把這一切兜起來:屏蔽若沒良好接地,就會變成天線而非屏障。大量接地過孔、寬廣的縫合走線與可靠的焊點,都是好屏蔽的必要條件。

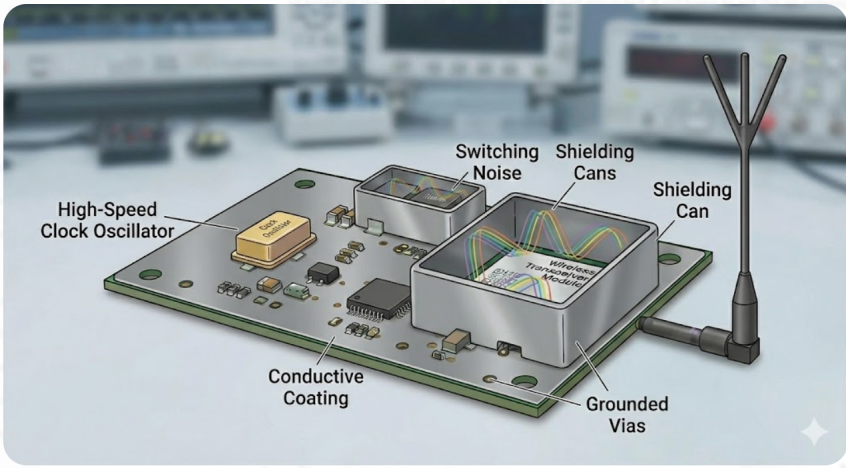

屏蔽層、屏蔽罩與導電塗層的角色

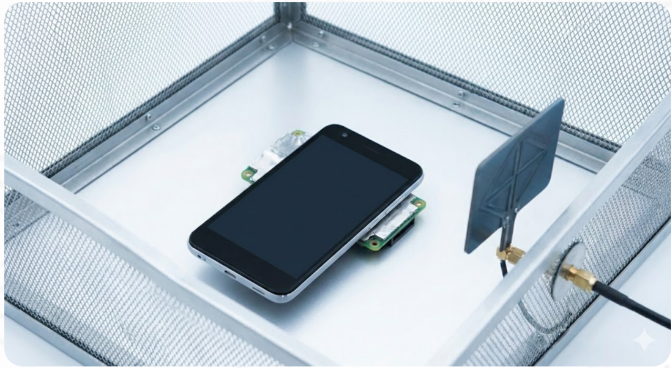

在板級,可依需求選擇不同屏蔽方式。屏蔽罩(shielding can)是直接焊在 PCB 上的金屬外殼,覆蓋敏感元件,常見於射頻模組、無線設備與敏感類比電路,材料多為鍍錫鋼或鎳銀,衰減可達 40–80 dB。若對重量或高度有限制,可改用輕薄導電塗層或導電漆,內含金屬顆粒(銀、銅、鎳)與聚合物,可局部噴塗。

PCB 內部則靠連續的接地銅面當內建屏蔽層。在雜訊層與敏感電路之間放一層完整無分割的接地平面,可大幅降低耦合雜訊,是最便宜也最容易實現的板級屏蔽法之一。

關鍵 EMI 屏蔽材料及其應用

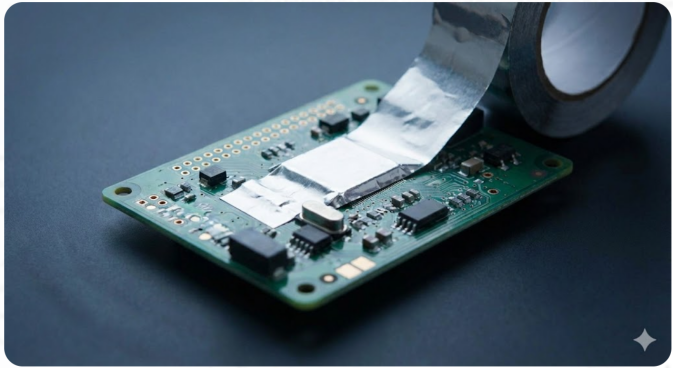

導電布、導電箔與聚合物複材

在實驗室或維修現場,銅箔膠帶因高導電且易施工仍是首選;若進入量產,可考慮金屬化纖維編織的導電布,具彈性且能貼合複雜外形。

含碳纖、鍍鎳顆粒或銀片的導電聚合物複材,兼具機械強度與屏蔽效能,可射出成任何外殼形狀,常見於消費性產品機構級屏蔽。

銅灌、接地平面與特用塗層

在 PCB 內部,銅灌與接地平面是最經濟的屏蔽手段。以 4 層板為例,將第 2 層完整當接地平面,可擋住頂層晶片對內層訊號或電源的干擾。訣竅在於保持平面完整,別讓縫隙、孔洞成為電磁洩漏路徑。

外層銅灌(copper flood)雙重目的:增加回流路徑與屏蔽,同時讓電鍍更均勻。重點是乾淨連回主接地網,並用足夠過孔縫合。

依頻段選材

不同頻段策略不同。<1 MHz 重點在磁場屏蔽,需高導磁合金(如 mu-metal 或鐵氧體)。MHz 至低 GHz 用銅或鋁即可反射兼吸收。>10 GHz 則重視加工精度,任何孔洞都可能成諧振腔。100 MHz–6 GHz 區間,一般銅平面與設計良好的屏蔽罩已足夠。重點不是用多貴材料,而是把縫隙封好、接地做好、開孔控制好。

專業提示:板上最高頻訊號決定屏蔽需求。記得 100 MHz 方波在 5、7、9 次諧波(500 MHz、700 MHz、900 MHz)仍有顯著能量,請針對諧波而非僅基頻做屏蔽。

在 PCB 設計中落實有效 EMI 屏蔽

分區、Via Fencing 與接地策略

控制輻射從佈局就開始。先把板子切成數位、類比、射頻、電源等區塊,讓雜訊源遠離敏感電路,先切斷耦合路徑。Via fencing(過孔圍籬)像用接地過孔築牆,只要過孔間距小於最高頻波長的十分之一,就能在板級形成電磁屏障。

接地策略同樣關鍵:採星形或分割接地,讓各區回流路徑獨立並於單點匯合,避免雜訊電流拖曳其他區域。

與多層疊構及元件擺放的整合

疊構本身就是第一道防線。在良好的 多層 PCB 中,每個訊號層都緊鄰接地或電源平面,讓迴路面積最小並自帶層間屏蔽。六層 EMC 優化疊構可採 Signal-Ground-Signal-Power-Ground-Signal,使高速走線隨時有參考平面。元件擺放則配合分區:時脈、切換穩壓器、高速處理器放數位區,走線短且直;射頻與敏感類比區盡量遠離,電源進入端即做濾波。

專業製程打造可靠 EMI 屏蔽

屏蔽層與塗層的精準施工

想讓 EMI 屏蔽到位,製程精度是關鍵。屏蔽罩必須焊得紮實無空孔,任何細縫都可能變成槽縫天線。導電塗層需控制厚度(通常 5–75 µm)且均勻覆蓋,太薄屏蔽不足,太厚易龜裂剝離。專業噴塗加遮罩可確保邊緣整齊、厚度一致。

先進測試驗證合規與性能

EMC 認證測試包含輻射發射(CISPR 32/FCC Part 15)、傳導發射與輻射抗擾度。開發階段先用近場探棒與頻譜儀做預兼容測試,及早發現問題,避免認證時大翻盤。板級屏蔽效能可用傳輸阻抗、屏蔽室或近場掃描量化,找出弱點再對症下藥。

JLCPCB 如何量產可靠 EMI 屏蔽 PCB

JLCPCB 的多層板製程層間對位精準,確保接地平面連續;受控阻抗讓幾何一致,EMC 特性可預測。完整 DFM 檢查會先確認接地平面、via fencing、銅灌是否符合設計意圖。

在組裝端,SMT 產線能精準放置並焊接屏蔽罩,確保每處接地可靠。結合製板與組裝的精度,讓成品板出廠即可直接挑戰 EMC 測試。

常見問題 (FAQ)

Q. 什麼是 EMI 屏蔽?所有 PCB 都需要嗎?

EMI 屏蔽是用導電材料阻擋電磁干擾進出電路區塊。並非每塊 PCB 都需要金屬罩或塗層,但所有板子都該落實連續接地平面、妥當解耦與受控阻抗等基本 EMI 設計。

Q. 板級 EMI 屏蔽如何運作?

靠反射、吸收與良好接地(提供低阻抗回流路徑)三大機制協同。接地平面、via fencing 與實體屏蔽罩共同完成。

Q. PCB 最常見的 EMI 屏蔽材料?

銅、鍍錫鋼或鎳銀(屏蔽罩)、導電聚合物塗層。板內現成的銅只要善用,就是最便宜的屏蔽材料。

Q. Via fencing 能取代屏蔽罩嗎?

Via fencing 可提供中等屏蔽效果(約 15–30 dB),適合降低區塊間耦合;若需高隔離(>40 dB),仍得靠實體屏蔽罩。

持續學習

PCB電源與地平面設計實戰筆記

製造四層及以上PCB時,我們總會預留整層銅箔專門做電源和地,不少人覺得這樣太浪費,其實從電磁場原理來看,電源層和地層緊挨著,本質就是一個超大平板電容。這個容值不算大,但寄生電感特別低,對付高頻開關噪聲至關重要。按照電容計算公式,平面間距越小,層間耦合電容就越大,能有效壓低電源配電網絡的高頻阻抗,這也是電源層和地層必須盡量貼近的核心原因。 一、回流路徑:高速PCB信号完整性的核心 高速設計里有個關鍵常识:信号不是只在導線里傳輸,而是在導線和参考平面之間的介質中傳播。頻率超過100kHz後,回流電流不會走最短直線,而是貼著信号線下方的地平面形成鏡像電流,所以地平面必須保持完整。 注意事項:最忌諱地平面跨分割,比如為了區分模擬地和數字地,直接把地平面切開。一旦信号線跨過這個缺口,回流電流只能繞遠路返回,不僅會形成環路天線引發嚴重EMI干擾,還會因為阻抗不連續導致信号反射、波形畸變。 二、 接地實操:別糾結點接地,優先用面接地 接地不用在“點”和“面”里反複糾結,直接按場景選就行: 低頻、精密模擬電路,用星形接地,避免大電流回路干擾小信号; 高速數字電路,必須用平面接地,大面积地平面能把電感壓到極低。 實......

駕馭阻抗版圖:為 USB、乙太網路、HDMI 與 SD 卡介面選擇合適阻抗

1- 簡介: 在高速數位通訊領域,選擇正確的阻抗是 PCB 設計成功的關鍵。阻抗匹配可確保訊號完整性、將反射降至最低,並提升 USB、乙太網路、HDMI 與 SD 卡等介面的整體效能。本文將探討阻抗的重要性、影響阻抗選擇的因素,以及確保這些常用介面可靠資料傳輸的最佳實務。 2- 認識數位介面中的阻抗: 阻抗以歐姆為單位,是衡量電路對交流電(AC)阻礙程度的關鍵參數。在高速數位介面中,維持正確的阻抗對於防止訊號反射、降低串擾並確保傳輸資料的完整性至關重要。 3- USB(通用序列匯流排): A- USB 2.0: 標準阻抗: 90 歐姆 最佳實務: 為 USB 2.0 資料線使用受控阻抗走線,以防止訊號失真並確保可靠通訊。 B- USB 3.x: 差動阻抗: 90 歐姆 單端阻抗: 45 歐姆 最佳實務: 在整個 USB 3.x 訊號路徑(包括連接器與纜線)上維持一致的阻抗特性,以支援高速資料傳輸。 4- 乙太網路: 10/100/1000BASE-T(乙太網路): 差動阻抗: 100 歐姆 最佳實務: 確保整條傳輸線的阻抗一致,避免訊號劣化並維持訊號完整性。 5- HDMI(高畫質多媒體介面): ......

理解 PCB 設計中的類比接地與數位接地

在進行印刷電路板(PCB)設計時,良好的接地對於確保訊號完整性、降低雜訊並維持可靠效能至關重要。PCB 佈局中常用的兩種接地平面為類比地與數位地。本文將探討類比地與數位地的差異、其在 PCB 設計中的重要性,以及實作時的最佳做法。 1. 類比地與數位地 類比地與數位地在 PCB 設計中各自扮演不同角色,通常會予以隔離,以避免類比與數位訊號互相干擾。 類比地:類比地專供處理連續、變化且低速訊號的類比元件與電路使用。類比地對於維持訊號忠實度、降低雜訊並保持類比量測的準確性不可或缺。通常會將類比地與數位地隔離,防止數位(高速)雜訊污染並影響類比訊號。 數位地:數位地專供處理二進位開關訊號的數位元件與電路使用。數位地對於提供數位訊號的參考點、管理切換雜訊並防止數位電路中的接地迴路至關重要。與類比地類似,數位地通常也會與類比地隔離,以最小化兩者間的干擾。 2. 接地平面佈局 在 PCB 設計中,類比與數位接地平面通常以 PCB 基板上的銅平面實作。 這些接地平面為回流電流提供低阻抗路徑,並作為訊號傳播的參考平面。 ● 隔離:類比與數位接地平面應在 PCB 佈局中物理分隔,以最小化類比與數位訊號間的耦合。可透......

在混合訊號 PCB 設計中實現和諧

在電子世界中,由於技術演進,現今已普遍在同一塊電路板上混合類比與數位元件。混合訊號 PCB 設計象徵類比與數位領域的和諧結合,為精密電子裝置開啟無限可能。本文將探討混合訊號 PCB 設計,涵蓋其挑戰、最佳實踐,以及達成最佳效能的重要考量。 混合訊號設計的本質 混合訊號設計指的是在同一塊印刷電路板(PCB)上同時整合類比與數位電路。類比元件處理連續訊號,例如音訊或感測器輸入。數位元件則處理離散訊號,常見於微控制器或數位訊號處理器。這些不同元素的融合創造出混合訊號環境,使複雜且多功能的電子系統得以實現。 混合訊號 PCB 設計的挑戰: A- 訊號完整性: 平衡類比與數位訊號的需求是一項精細的任務。高速數位訊號可能引入雜訊與干擾,影響類比元件的準確度。謹慎的走線、接地平面設計與訊號隔離對維持訊號完整性至關重要。 B- 串擾: 當類比與數位訊號過於接近時,可能產生串擾,進而干擾不同區域的訊號。適當的佈局與遮罩技術對於降低串擾並防止不必要的交互作用不可或缺。 C- 電源分配: 混合訊號設計通常需特別關注電源分配。數位元件可能產生快速的電源瞬變,進而影響類比元件。劃分電源域、使用專用電源平面,並採用適當的去耦......

現代電子設計的動力心臟:2026 電源模組選型與高效 PCB 電源佈局實務

硬體開發目前面臨著前所未有的挑戰:在不斷縮小的PCB板空間內,必須確保可滿足運算效能激增帶來的巨大電流需求。穩定且高效的電源管理方案,已成為目前工業級設備製造的關鍵。對於工程師而言,電源模組的應用不只是為了節省空間,更是在複雜的電磁環境中,確保電子板具備極致的供電品質。 在實現高密度功率設計的過程中,精密的製造工藝是成功的前提。作為全球領先的電子製造商,JLCPCB 擁有先進的PCB製造設備與技術支持。無論您是採購高品質的電子元件,還是尋求一站式的SMT組裝,JLCPCB都能全力提供最具競爭力的PCB報價,協助您的設計在穩定性與成本效益間達成完美平衡。 電源模組在高密度設計中的戰略地位 與傳統由分立電子零件搭建的直流轉換電路(如 Buck/Boost Converter)相比,現代集成式電源模組展現了顯著的工業優勢。 1. 瞬態響應與控制迴路優化 集成模組將控制器、驅動迴路和功率MOSFET共封裝在一起,極大地縮短了內部反饋路徑的物理距離。物理距離的縮短能增大整個系統瞬間負載變化的響應速度,對現今高工作頻率的處理器意義重大。 2. 熱設計功耗 (TDP) 的優化分配 高品質的電源塊一般都是選高導熱......

什麼是衰減:訊號如何隨距離減弱

當訊號從源頭經由 PCB 導體傳送到負載時,會因走線電阻與介電損耗而衰減,導致能量損失。訊號衰減是高速訊號在電路板上傳輸時最常見的術語。 它是造成訊號劣化的主要原因之一,進而引發訊號完整性問題。通常頻率越高衰減越明顯,這與集膚效應等現象有關。 衰減係數決定了訊號在仍能提供足夠資料位元或資訊的前提下可傳輸多遠。它量化了不同傳輸介質如何隨頻率降低傳輸訊號的振幅,公式如下: AF = P 輸出 / P 輸入 訊號衰減係數取決於: 傳輸介質長度 傳輸介質材料 物理條件 什麼是衰減?意義與定義 衰減是訊號在介質中傳播時振幅減小的現象,可能由傳輸損耗、反射或吸收造成。在電氣系統中,衰減指的是電壓沿導線或其他傳輸線流動時的下降。衰減的系統也可稱為劣化系統。 衰減以分貝(dB)表示,代表輸出與輸入功率或強度的比值。衰減值可從無阻礙或完美傳輸的 0 dB,到極大的負數。一個完美的衰減器若為 0 dB,表示在傳輸線上有無限多個抽頭。 不同類型的可變衰減器: 訊號或纜線衰減的原因 談到訊號或纜線衰減,我們指的是發射端與接收端之間的訊號劣化。訊號損失可能由影響纜線品質的多種變數引起,例如: 光纖製造不良(連接器不良與熔接......