陶瓷四邊扁平封裝(CQFP):設計、可靠性、組裝與使用時機

3 分鐘

- 什麼是陶瓷四邊扁平封裝(CQFP)?

- 為何 CQFP 在高可靠度電子中仍不可或缺

- 陶瓷四邊扁平封裝(CQFP)vs 塑膠四邊扁平封裝(PQFP):工程師必知的關鍵差異

- 何時該選用 CQFP 封裝?

- CQFP 封裝如何製造?

- CQFP 封裝尺寸、引腳數與外形

- CQFP 封裝 PCB 腳位設計指南

- CQFP 封裝如何處理熱與熱循環?

- 使用 CQFP 封裝常見工程錯誤

- CQFP 封裝的組裝挑戰有哪些?

- JLCPCB 如何可靠處理 CQFP 組裝

- CQFP 組裝的 DFM 建議

- 結論

- 常見問題:陶瓷四邊扁平封裝(CQFP)

當系統故障不可接受時,IC 封裝的選擇就成為以可靠度為導向的工程決策,而非僅以成本為考量。在這種情境下,塑膠 IC 封裝在持續熱應力、振動與惡劣環境暴露下的限制很快就會浮現。

這正是陶瓷四邊扁平封裝(CQFP)仍被刻意選用的原因。與塑膠 QFP 不同,CQFP 提供氣密封裝、優異的尺寸穩定性與可預測的長期老化特性,這些對航太、太空、國防及其他高可靠度電子產品至關重要。

本文將深入探討 CQFP 與塑膠封裝的真正差異,包括內部結構、材料系統、PCB 腳位設計考量、組裝挑戰與熱性能,協助工程師判斷何時必須採用 CQFP,何時不需要,讓可靠度裕度不再憑空假設。

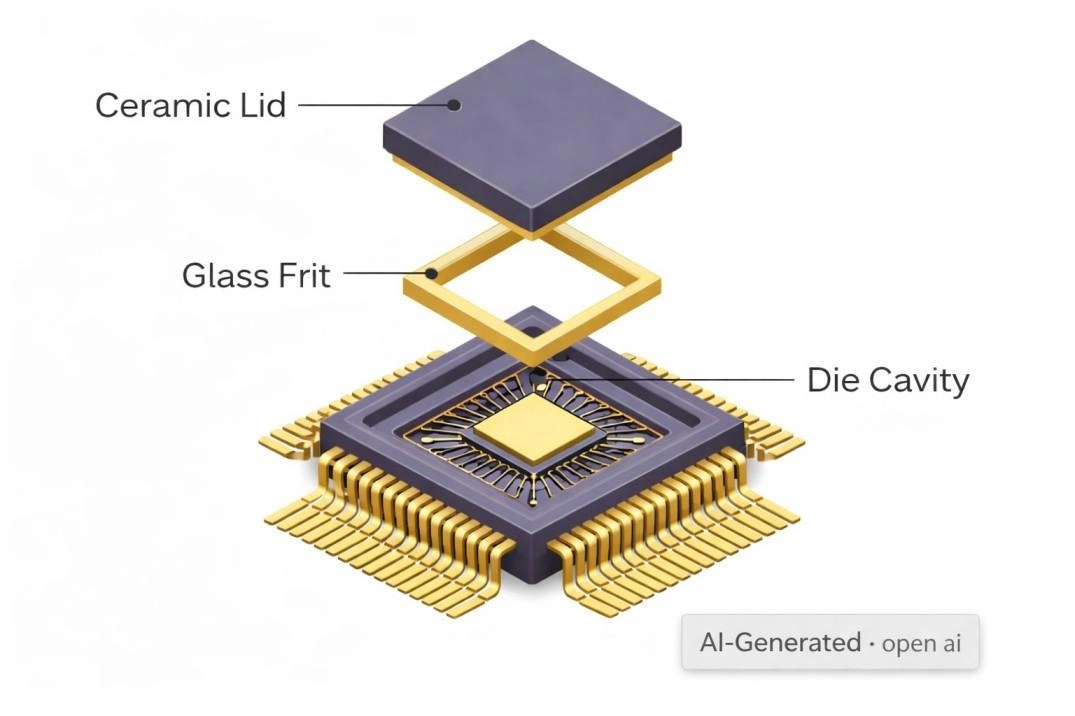

Ceramic Quad Flat Package CQFP-132 IC package

什麼是陶瓷四邊扁平封裝(CQFP)?

陶瓷四邊扁平封裝(CQFP)是一種表面黏著 IC 封裝,具備陶瓷本體與四邊鷗翼型引腳,專為高可靠度電子設計。與塑膠 QFP 不同,CQFP 採用氣密封裝,可長期隔絕濕氣與環境汙染。

CQFP 內部將晶粒固定於陶瓷基板,並以陶瓷或金屬蓋板透過玻璃釉或銲料密封。此結構可避免塑膠封裝常見的吸濕、膨脹與材料老化,特別在高溫與長壽命應用中。

因其成本高、組裝要求嚴格,CQFP 並非為了製造便利而使用,而是刻意用於航太、太空及其他任務關鍵應用,這些場合必須確保可預測老化、熱穩定性與數十年可靠度。

CQFP internal structure

CQFP 封裝技術規格

| Property | Typical Value / Material | Industry Standard |

|---|---|---|

| Body Material | High-purity Alumina (90–92%) | Verified per ASTM D116 |

| Seal Type | Hermetic (Glass Frit or AuSn Solder) | MIL-STD-883, Method 1014 |

| Lead Frame | Kovar (Fe-Ni-Co) or Alloy 42 | ASTM F15 |

| CTE (Ceramic) | ~6.5 to 7.0 ppm/℃ | Substrate only, matches silicon |

| Moisture Sensitivity | MSL 1 (Unlimited Floor Life) | J-STD-020 |

為何 CQFP 在高可靠度電子中仍不可或缺

CQFP 封裝在長期可靠度限制塑膠 IC 應用的場合仍被採用。在航太與太空系統中,寬溫度範圍、振動與數十年服役壽命使氣密封裝與陶瓷尺寸穩定性成為必要條件。

CQFP 亦被用於高溫工業環境,持續高熱會加速塑膠封裝的濕氣滲入、材料老化與機械潛變。雖然 CQFP 增加成本與組裝複雜度,但在可預測老化與環境隔離至關重要時,其成本可被合理化;若無這些需求,CQFP 通常非必要。

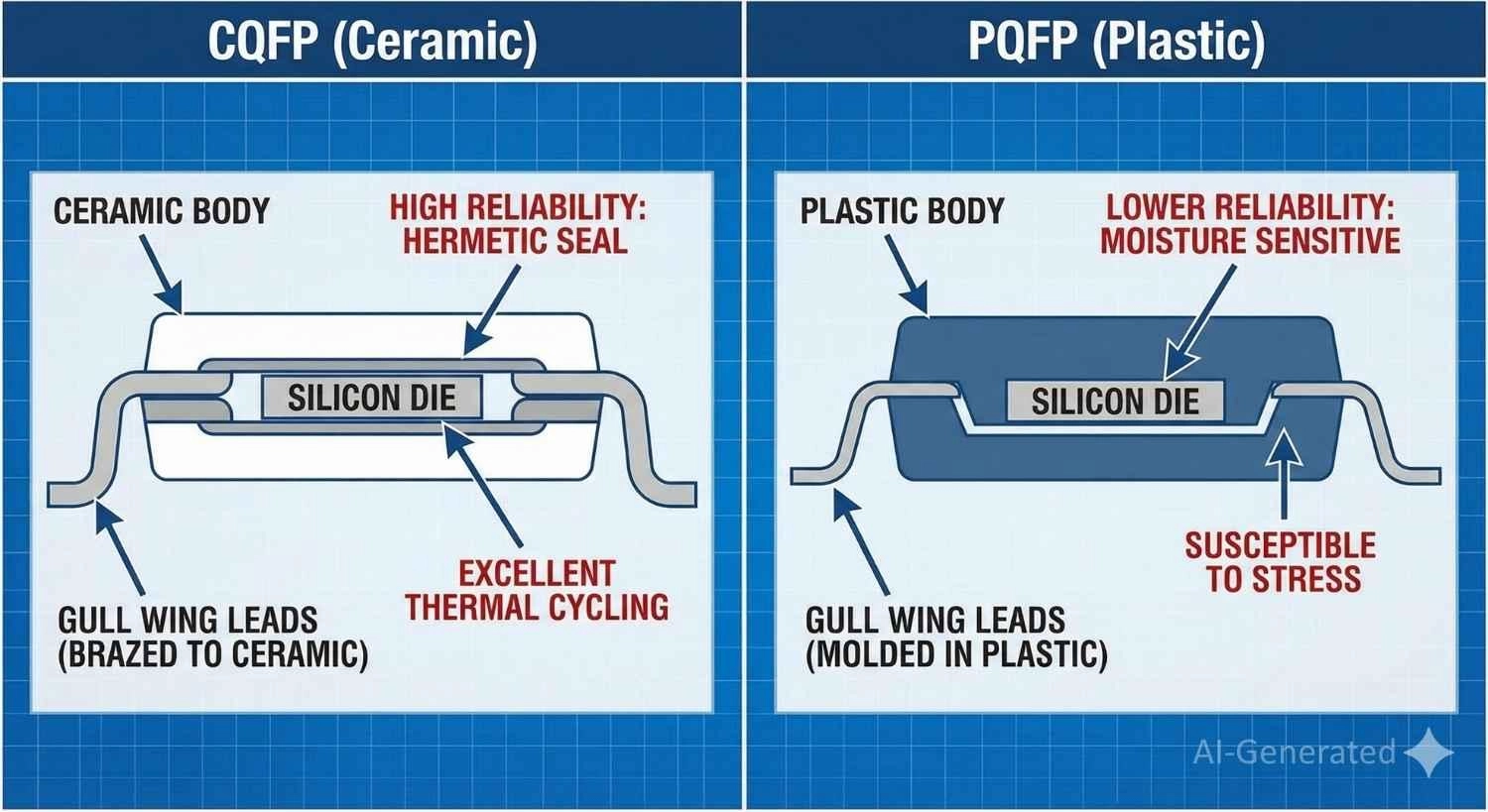

陶瓷四邊扁平封裝(CQFP)vs 塑膠四邊扁平封裝(PQFP):工程師必知的關鍵差異

| Parameter | CQFP (Ceramic QFP) | Plastic QFP (PQFP) |

|---|---|---|

| Body Material | Ceramic substrate with sealed cavity | Epoxy molding compound |

| Moisture Protection | Hermetic, typically MSL 1 | Moisture permeable |

| Thermal Stability | Stable across wide temperature range | Degrades at elevated temperature |

| CTE (ppm/°C) | 6–7 (closer to silicon) | 15–25 (mismatch causes stress) |

| Long-Term Aging | Minimal change over the decades | Noticeable over time |

| Assembly Cost | Higher, due to materials and tighter process control | Lower, optimized for volume |

| Typical Applications | Aerospace, space, high-reliability industrial | Consumer and standard industrial |

工程師重點整理:

CQFP 刻意用於長期可靠度、氣密保護與熱穩定性至關重要的環境。塑膠 QFP 在成本敏感的大量應用中表現優異,但其環氧本體會吸濕、在高溫下潛變,並隨時間將應力傳遞至焊線。

CQFP 的關鍵差異:

● 氣密封裝 避免濕氣相關失效

● CTE 匹配 矽片降低熱疲勞

● 穩定材料特性 確保數十年可預測老化

簡言之,CQFP 並非為成本或組裝便利,而是在不容失效處保證性能。

CQFP 結構以數十年熱、機械與環境應力下的可靠度為優先,成為航太、太空與高可靠度工業系統的首選,而塑膠封裝無法滿足其壽命要求。

何時該選用 CQFP 封裝?

| Condition | Recommendation |

|---|---|

| Hermetic sealing required | CQFP preferred |

| Long-term thermal stability needed | CQFP preferred |

| Operation in harsh environments (humidity, vibration, high temp) | CQFP preferred |

| Service life of 10–30+ years | CQFP preferred |

| Cost-sensitive, high-volume production | Plastic QFP preferred |

| Simple assembly or benign conditions | Plastic QFP sufficient |

總結: 僅當可靠度、環境耐受與長壽命超越成本與組裝複雜度時,才選 CQFP。對於一般消費或工業應用,塑膠 QFP 仍較實用。

CQFP vs PQFP internal frame, showing the difference between ceramic hermetic sealing and plastic encapsulation

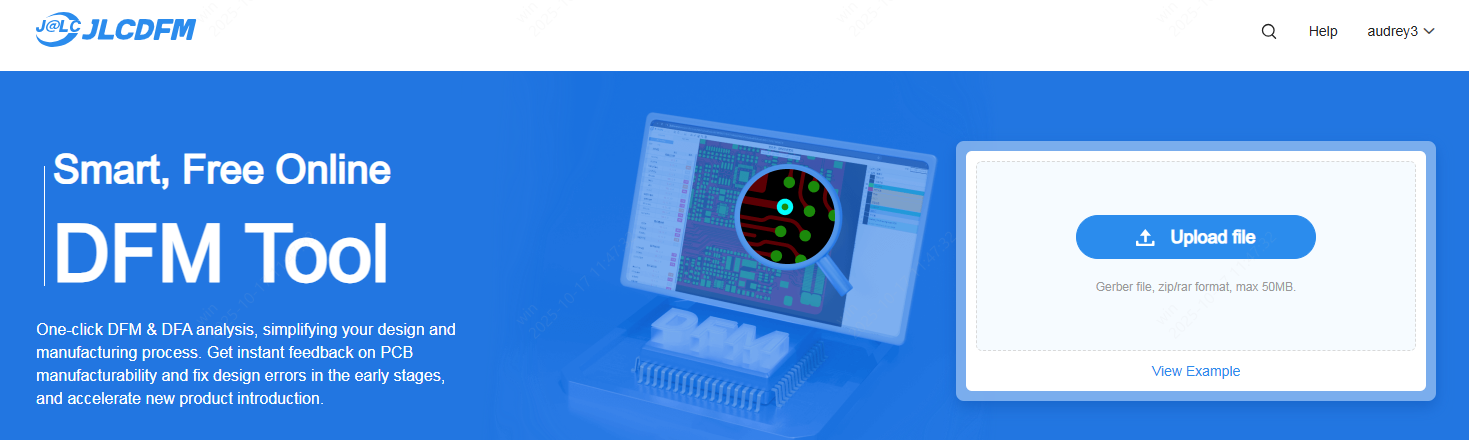

專業提示:

CQFP 陶瓷封裝剛性高、價格昂貴,對腳位誤差零容忍。

在發布布局前,強烈建議執行針對焊墊幾何、引腳間距與銲料填角裕度的 DFM 檢查。及早發現問題,可避免高可靠度陶瓷組裝的昂貴重工或報廢。

JLCPCB 提供 免費線上 DFM 工具,可在布局階段驗證這些細節。

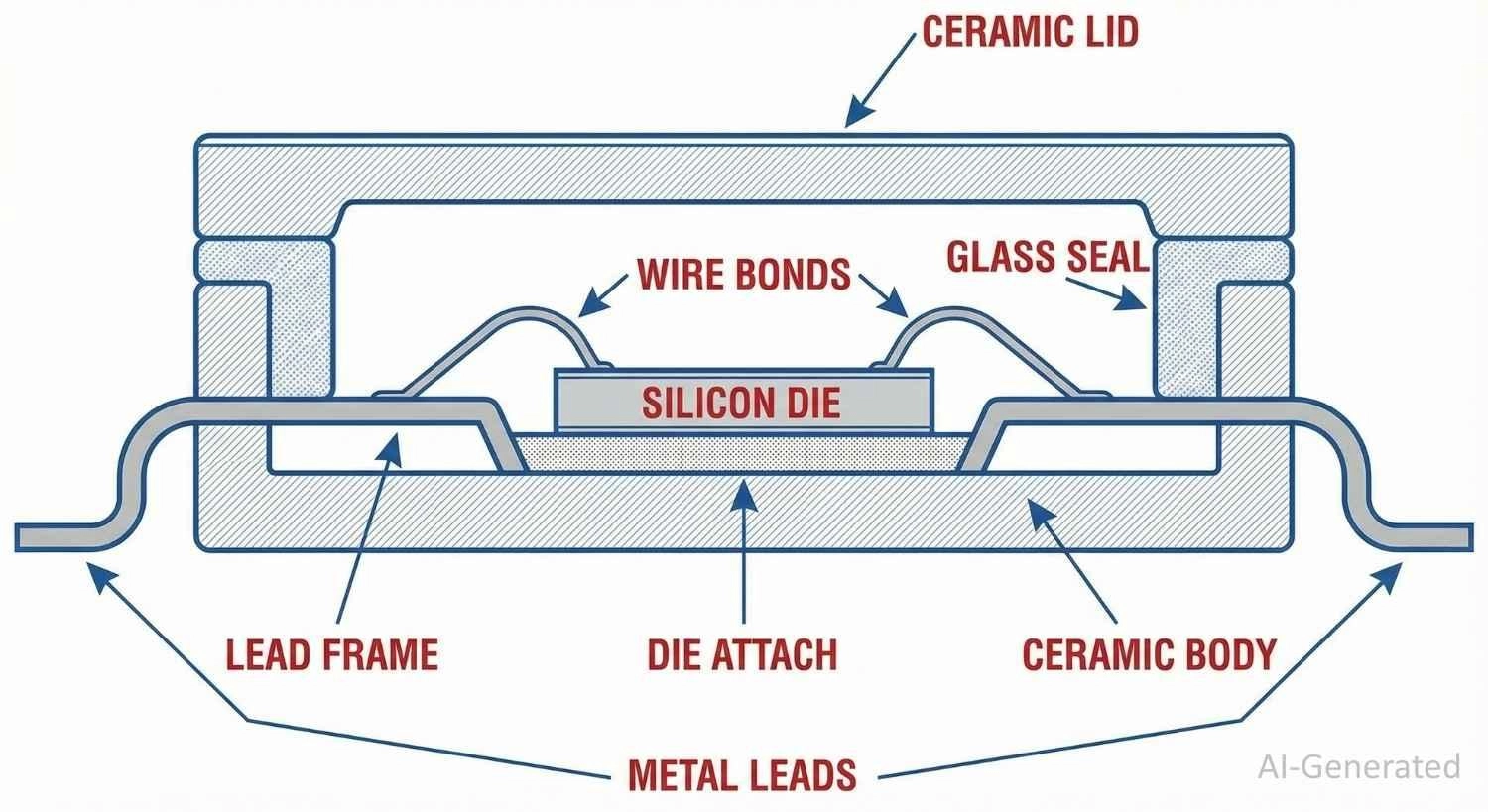

CQFP 封裝如何製造?

CQFP package structure

CQFP 的可靠度直接來自其結構與材料。每個元件都為長期熱與機械穩定性挑選,確保數十年可預測性能。

1. 陶瓷本體與基板

核心為高純度氧化鋁或多層陶瓷基板,提供尺寸穩定性、高剛性與低熱膨脹,在反覆熱循環中維持晶粒、焊線與引腳對位。穩定的介電特性適合精密類比與混合訊號設計,抗濕與抗汙染則支援長壽命。

2. 晶粒黏著與焊線

晶粒以金基黏晶膠或導電環氧膠固定於陶瓷基板,電氣連接採用耐腐蝕的金焊線,確保長期可靠度。剛性陶瓷底座將機械應變降至最低,相較塑膠 QFP 大幅降低熱循環疲勞。

3. 氣密封裝

CQFP 具氣密封裝腔體,以陶瓷或金屬蓋板透過玻璃釉或銲料密封,隔絕濕氣、腐蝕與參數漂移,維持 MSL 1 等級。氣密性亦確保真空環境相容與電離輻射防護,對航太與太空應用至關重要。

4. 引腳與金屬化

引腳採用 Kovar(Fe-Ni-Co)或銅合金,具可控熱膨脹與機械耐久性,表面電鍍確保銲錫性,設計可承受振動、衝擊與熱循環,長期維持機械完整性。

CQFP 封裝尺寸、引腳數與外形

CQFP 封裝僅提供有限製造商定義外形,通常與航太或高可靠度認證計畫掛鉤,而非開放大量標準。相較塑膠 QFP,選項較少,反映陶瓷結構與氣密封裝的限制。

| Parameter | Engineering-Relevant Characteristics |

|---|---|

| Pin Count | 常見於中到高引腳數元件(約 44 至 200 腳),確切規格取決於供應商與認證等級 |

| Lead Pitch | 多數 CQFP 採 1.27 mm(50 mil)或 0.635 mm(25 mil)間距;更細間距存在但較少且控管嚴格 |

| Body Size | 因陶瓷基板與密封腔體,整體尺寸大於同級塑膠 QFP |

| Package Height | 整體高度較高,由陶瓷底座與氣密蓋板造成 |

| Dimensional Tolerance | 批次間控制更嚴,翹曲與機械變異低於大量市售塑膠封裝 |

由於 CQFP 常用於航太與太空認證計畫,製造商規格書與外形圖必須視為唯一依據。

僅參考標稱封裝尺寸不足以設計腳位。引腳幾何或本體尺寸的微小偏差,都會顯著影響陶瓷封裝的銲點成形與長期可靠度。

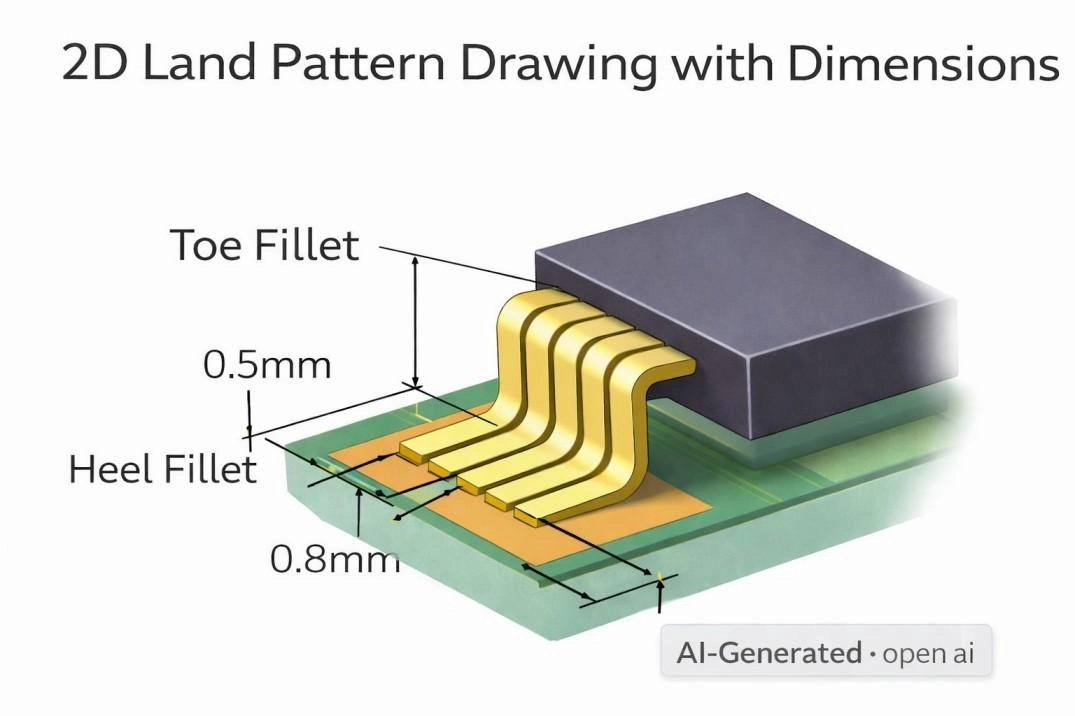

CQFP 封裝 PCB 腳位設計指南

為 CQFP 設計 PCB 腳位需有別於塑膠 QFP 的思維。陶瓷封裝機械剛性高,無法透過封裝變形吸收應力。

因此,熱膨脹不匹配與機械負荷幾乎完全傳遞至銲點。對 CQFP 而言,腳位精度是可靠度驅動因素,而非僅組裝問題。

為何 CQFP 腳位更敏感

與塑膠 QFP 不同,CQFP 本體在回銲或熱循環中不會彎曲。陶瓷封裝、銅墊與 PCB 基材間的差異膨脹,應力集中於銲點的腳跟與腳尖區域。塑膠封裝可容忍的焊墊長度、引腳對位或共面微小誤差,在 CQFP 組裝中可能加速疲勞裂紋。

因此,CQFP 對通用或「沿用」QFP 焊墊圖案的容忍度較低。初期檢查通過的設計,在長期熱循環或振動後仍可能出現接點劣化。

CQFP PCB land pattern design dimensions and solder mask dams

CQFP 專用焊墊與腳位設計準則

● 無替代地採用製造商建議腳位。對 CQFP 而言,規格書尺寸優於 IPC 預設值。

● 避免過大焊墊。過多銲錫體積增加接點剛性,提高腳跟循環應力。

● 控制焊墊長度以平衡腳尖與腳跟填角。過長焊墊會移動接點中性點並降低疲勞壽命。

● 焊墊寬度緊配引腳寬度,減少側向銲錫流動,有助回流時維持引腳共面。

● 採用保守綠漆開口。細間距處需良好綠漆壩,防止橋接與不均填角。

● 及早確認 courtyard 與檢修通道。陶瓷剛性與引腳強度使 CQFP 重工容忍度較低。

將塑膠 QFP 腳位直接用於 CQFP,是高可靠度應用長期失效的常見根本原因。雖然此類設計可能初期組裝成功,但陶瓷封裝的機械行為使這些捷徑在高可靠度應用中風險極高。對 CQFP 組裝而言,腳位正確性與產品壽命密不可分。

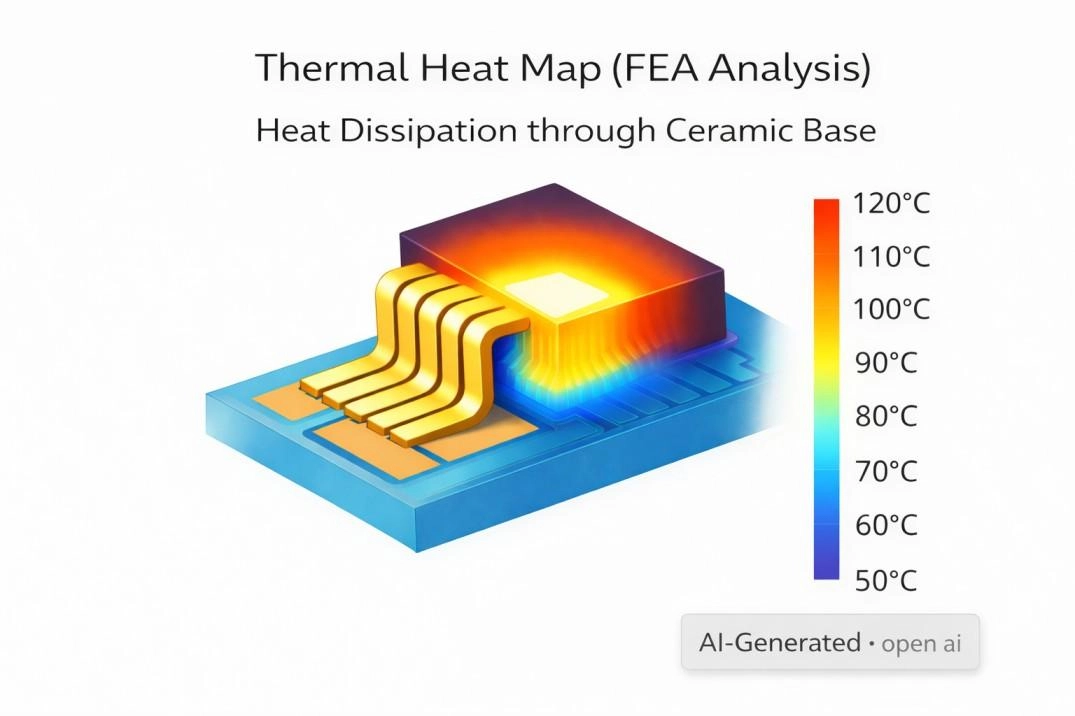

CQFP 封裝如何處理熱與熱循環?

CQFP 封裝適合高溫與反覆熱循環為常態的環境。陶瓷本體在高溫下仍保持機械穩定,不會隨時間潛變或軟化,避免塑膠 IC 封裝的漸變形變。

雖然熱膨脹仍會產生應力,陶瓷的剛性可防止應力透過封裝變形累積,使銲點負荷更可預測,並提升長期疲勞阻抗。

此外,陶瓷基板保持穩定熱導率,使晶粒至外殼的熱行為在長期運作中保持一致。

CQFP thermal resistance junction-to-case heat dissipation analysis

使用 CQFP 封裝常見工程錯誤

即使經驗豐富的工程師,若忽略 CQFP 特定要求,也可能遭遇可靠度問題。常見錯誤包括:

1. 沿用塑膠 QFP 腳位 – 忽略陶瓷專用焊墊幾何,導致銲點疲勞或橋接。

2. 忽略 CTE 不匹配 – 未考量陶瓷與 PCB 間差異膨脹,加速接點疲勞。

3. 套用通用回銲曲線 – 為塑膠封裝調校的曲線可能過熱或欠銲陶瓷引腳。

4. 低估組裝複雜度與成本 – 假設陶瓷行為類似塑膠,可能導致意外失效與報廢增加。

5. 跳過陶瓷剛性的 DFM 或檢查 – 缺預產審查可能遺漏影響長期可靠度的細微設計錯誤。

CQFP 封裝的組裝挑戰有哪些?

CQFP 封裝因剛性陶瓷本體與氣密結構,行為與塑膠 QFP 不同。主要組裝限制包括:

● 製程裕度有限 – 陶瓷封裝不會彎曲吸收置件誤差,微小偏移直接反映在銲點。

● 回銲熱敏感度 – 急速局部加熱可能導致應力或破裂;回銲曲線須匹配陶瓷熱容量。

● 重工限制 – 局部銲接或熱風重工風險較高,易損壞封裝或引腳。

● 引腳共面與銲錫潤濕 – 引腳高度或焊墊幾何偏差容忍度低於塑膠 QFP。

總之,CQFP 組裝需更嚴製程控制、精準置件與遵循建議熱曲線。具備陶瓷封裝經驗可顯著提升良率與可靠度。

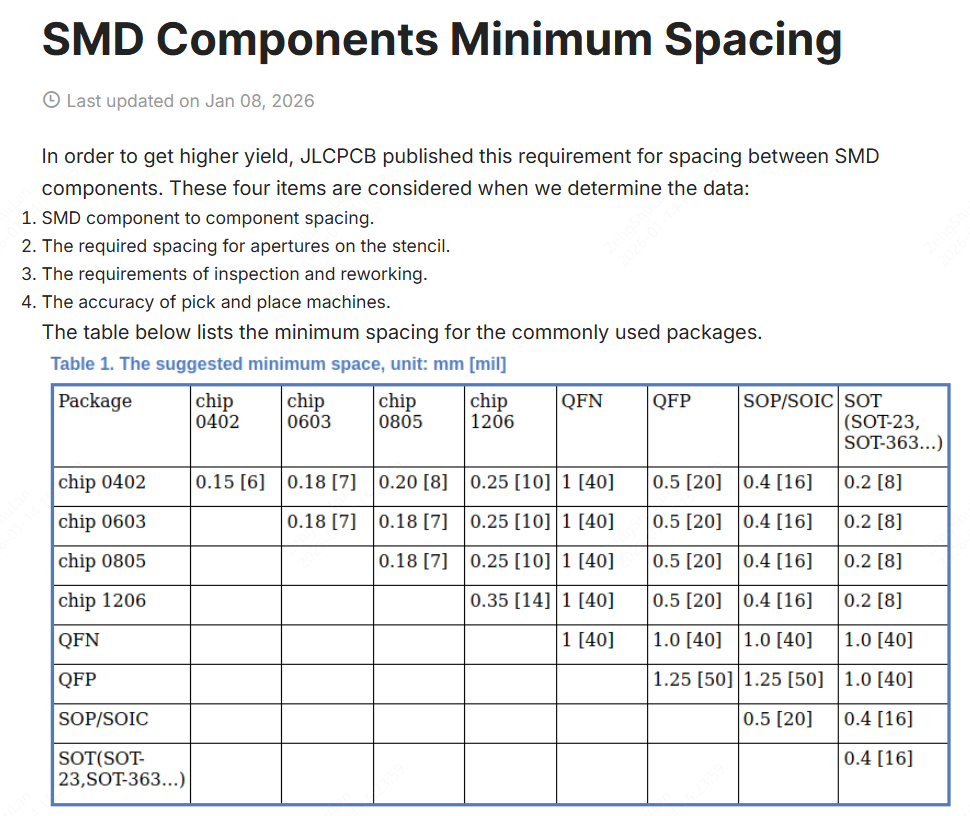

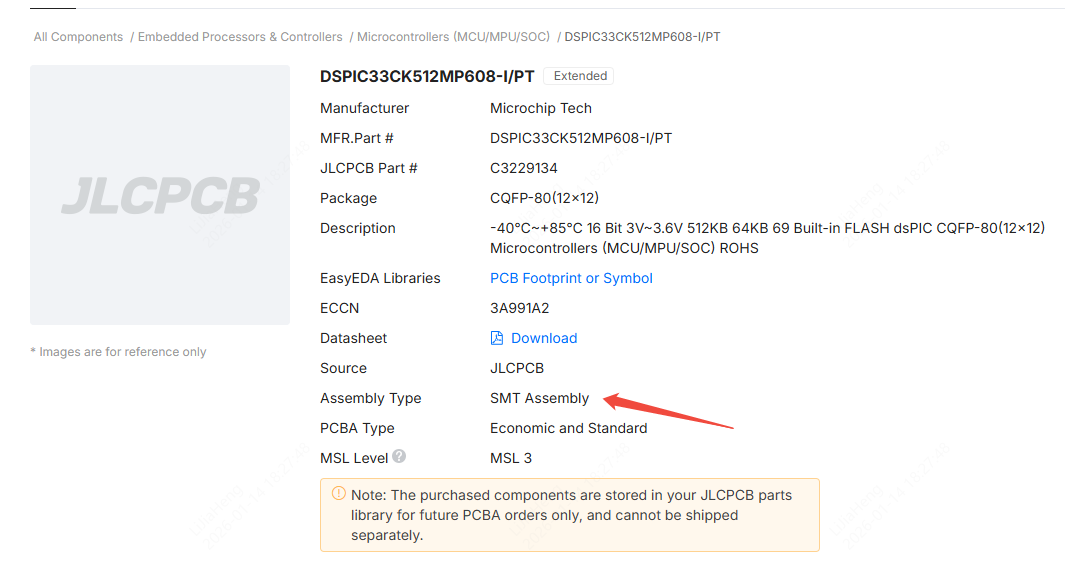

JLCPCB 如何可靠處理 CQFP 組裝

JLCPCB 的 SMT 組裝製程透過遵循表面黏著元件最小間距規範,可靠支援 0.5 mm 引腳間距 CQFP 封裝。

這些間距規則考量元件間隙、鋼板開口、檢修與重工空間,以及自動取放機精度,確保 CQFP 等細間距 IC 的可製造性。

透過維持足夠間距與成熟組裝協議,JLCPCB 降低銲橋與偏移風險,為採用 CQFP 及其他細間距封裝的電路板提供一致高品質結果。

延伸閱讀:Minimum spacing requirements for SMD components

CQFP 組裝的 DFM 建議

CQFP 封裝因剛性陶瓷與氣密結構,需精確 DFM 規劃。重點如下:

● 焊墊幾何與綠漆 – 確保焊墊長寬支援強健填角;維持綠漆壩防橋接。

● 引腳共面與間隙 – 檢查引腳高度一致與檢修空間。

● 回銲曲線與熱容量 – 調整銲接曲線以配合陶瓷較慢熱吸收。

● 早期 DFM 驗證 – 利用 JLCPCB 設計檢查,在製造前發現腳位、銲接或間隙問題。

合規: 符合 MIL-PRF-38535、MIL-STD-883 與 NASA-STD-8739.3,滿足高可靠度與航太級要求。

遵循這些建議可減少組裝失效、提升良率,並確保 CQFP 系統長期可靠度。

結論

陶瓷四邊扁平封裝(CQFP)仍是需要氣密封裝、熱穩定性與數十年壽命的高可靠度電子首選。

雖然比塑膠 QFP 昂貴且組裝要求高,其可預測的機械、熱與環境特性,確保在航太、太空與嚴苛工業應用中的長期性能。

設計者應仔細考量腳位、DFM 與熱管理,以充分發揮 CQFP 優勢,確保長期穩健可靠的系統運作。

常見問題:陶瓷四邊扁平封裝(CQFP)

1. CQFP 可直接取代塑膠 QFP 嗎?

不行。雖然外觀相似,CQFP 在機械剛性、熱行為與組裝需求上皆不同。未重新設計直接替換,常導致銲點疲勞、焊線應力與長期可靠度問題,特別是在航太或工業系統。

2. CQFP 封裝對濕氣敏感嗎?

不會。多數 CQFP 為氣密封裝,MSL 1 等級,本質抗濕。與塑膠 QFP 不同,即使在濕熱或高溫環境,仍保持穩定電氣與機械性能,對長期嚴苛或太空級應用至關重要。

3. 為何 CQFP 比塑膠 QFP 貴?

CQFP 成本高來自陶瓷材料、氣密封裝製程、更緊尺寸公差與少量生產。這些因素確保數十年可預測的機械與熱性能,為高可靠度電子、航太與工業系統所必需。

4. CQFP 需要特殊 PCB 腳位嗎?

需要。CQFP 腳位需保守焊墊幾何、精確綠漆設計與引腳對位。直接沿用塑膠 QFP 腳位可能導致銲點裂紋或組裝缺陷。正確的 CQFP 腳位設計對維持高可靠應用的長期可靠度與穩健性能至關重要。

持續學習

斷路器類型與應用完整指南

電路可能受損,導致可靠性降低。因此,電路需要使用保護裝置來保護。通常保險絲、扼流圈、去耦電容、齊納二極體、保護二極體就足以防止電子設備發生意外。斷路器在電氣系統中也用於相同目的。斷路器可定義為一種開關裝置,透過充當開關並中斷電流來防止電氣系統受損。本文將深入探討斷路器及其各種類型,研究其優缺點、運作原理等。 1. 什麼是斷路器? 斷路器是一種可手動或自動操作的開關機構,當偵測到電路中有異常電流或故障時,切斷電流,從而減少過載與短路情況。 斷路器與保險絲功能相同,但與保險絲不同,啟動或觸發時不會被破壞/燒毀。與保險絲不同,我們無需更換,只需在確認故障後重新設定即可。發生過載時,斷路器會開啟電路以防止任何損害。它們配有開關,可在跳脫後恢復閉合位置。斷路器廣泛用於家庭、工業和商業電氣設置,以保護設備免受損壞。 2. 如何選擇斷路器: 選擇斷路器時,需了解其規格。主要考量因素包括: 額定電壓:額定電壓是斷路器兩端可施加的最大電壓。需了解目標應用所需的電壓,並選擇電壓容量足以應對的斷路器。 連續電流額定值:要了解連續電流額定值,需確認安培數。安培額定值表示斷路器在不過熱的情況下可承受的連續電流。 頻率:要確......

微處理器與積體電路:主要差異、類型與應用

在電子領域中,一切源自矽,今天我們將討論兩種不同的矽晶片。這不是一場戰鬥,而是一場性價比的競賽。積體電路是一種半導體晶片,內部容納了數千到數十億個電晶體。積體電路將 MOS 電晶體的基本結構整合在一小片矽晶圓上。這些 MOS 電晶體以特定方式連接,實現了與更大電路相同的功能。這些 MOS 電晶體僅用於實現特定功能,無法被程式化,僅在電路連接時執行操作。然而,透過改變外部電路,單一積體電路可實現多種功能。 另一方面,微處理器是一個包含 CPU 及多個子 IC 的完整系統,可依指令進行程式化。在接下來的段落中,我們將深入探討。積體電路的起源可追溯至 1960 年代,將電路縮小至拇指大小的想法廣受歡迎,因為它能節省成本與空間,並改變多年來電子設計的方式。在本部落格中,我們將: 了解什麼是積體電路。 了解什麼是微處理器。 探討使用微處理器與積體電路設計時的挑戰。 1. 什麼是積體電路? 積體電路(有時稱為晶片或微晶片)是一種半導體晶圓,通常由矽製成,整合了包括電阻、電晶體、電容和二極體在內的電子電路,這些元件相互連接以執行特定功能。在積體電路出現之前,電晶體和電阻等元件需在電路板上焊接連接。隨著積體電路的......

什麼是電源管理 IC(PMIC):功能與應用

電源管理 IC(PMIC)是一種專門設計用來管理主機系統電源需求的積體電路。它能有效率地為裝置內的各種元件(如處理器、記憶體單元與周邊設備)分配、調節、轉換與監控電力。隨著對小型化、電池供電且高效能裝置的需求持續成長,PMIC 已成為跨產業系統設計中不可或缺的一環。嵌入式與應用處理器,以及其他複雜系統中的元件,都需要多組電源軌與多個電源域。請從這裡查看完整的 PCB 製造 流程。 在這類系統中使用離散元件進行電源管理成本高昂。將多組穩壓器與控制電路整合至單一晶片的電源管理積體電路(PMIC),是實現完整電源供應解決方案的理想選擇。它們可減少元件數量與電路板空間,同時以簡單且具成本效益的方式管理系統電源。本文將探討 PMIC 的定義、核心功能,以及其在現代電子領域的廣泛應用。 PMIC 如何運作? 半導體業界有時將 PMIC 類比為人體的「心臟」,「泵送」血液至各器官,使其維持功能。PMIC 扮演「電壓轉換器」的角色,將電池或電源端的電壓進行轉換,調整、協調並分配適當的電壓給電路中的每個元件。 PMIC 負責電源系統的電壓時序控制,為各種負載供電,並提供過壓、欠壓、過電流或其他熱問題的保護。因此,P......

理解 PCB 控制器在電子設計中的角色

PCB 控制器是設計與建構電氣系統的重要元件。它負責控制印刷電路板(PCB)上各種機械零件的功能,並確保彼此之間能順暢通訊。從家用科技到工廠自動化,PCB 控制器都有廣泛應用。本文旨在探討 PCB 控制器的重要性,涵蓋其種類、用途,以及選擇與使用的最佳實踐。 1. 什麼是 PCB 控制器? PCB 控制器是一種電腦元件,用於控制 PCB 的運作與功能。它通常包含微控制器或微處理器,以及記憶體晶片、電源管理單元與介面連接器等支援硬體。PCB 控制器的主要任務是讀取訊號並執行指令,協調板上其他元件的動作。統一控制能讓電子系統更高效且可靠。 2. PCB 控制器的類型 PCB 控制器依任務與效能需求不同,分為多種類型。以下是最常見的幾種: ⦁ 微控制器型控制器:這類控制器內建處理器,專門執行固定工作。低功耗與高彈性使其廣泛應用於家電與遙控器等消費性裝置。 ⦁ FPGA 控制器:現場可程式化閘陣列(FPGA)可隨時改變邏輯與行為,特別適合航太與工業環境中的複雜任務。透過程式設計即可隨時執行特定功能。 ⦁ 數位訊號處理器(DSP):專為高速完成複雜數學運算而設計,常見於音訊與視訊處理設備,如音響系統與視訊監......

電容器入門:它們如何運作、功能與類型

電容器是 PCB(印刷電路板)設計中不可或缺的元件,從儲能、濾波到穩壓皆扮演關鍵角色。無論是設計簡單電路或複雜多層板,了解不同類型的電容器及其應用都至關重要。電容器的基本結構由兩片金屬板中間夾一層介電質組成,可分為固定與可變兩種類型。 電容是電機工程的核心概念,代表系統儲存電荷的能力。電容器儲存電荷的能力稱為電容,單位為法拉。與電阻相同,電容器可串聯或並聯,進而改變總電容值。目前已開發出多種電容器供電子電路使用。本文將全面探討電容器的工作原理、功能、計算方法及各類型。想深入了解電子與 PCB 設計,請參閱我們最新的 PCB 製造流程 指南。 什麼是電容器及其工作原理? 電容器是被動元件,以電場形式儲存與釋放電能,由兩片導電板中間以絕緣介電質隔開。施加電壓時,金屬板會儲存電荷,兩板所帶電荷互補。電容器在電路中功能多元,其端子由金屬板引出供外部連接。 電容器的基本原理在於分離並儲存電荷。當連接電源時: 電子從負極流向其中一板(負極板),同時等量電子從另一板(正極板)被排斥至正極。 此電荷分離在介電質內建立電場,電容器持續充電,直到兩板電壓等於外加電壓。 充飽後,電容器可充當臨時電池,將電能儲存至電路需......

電子電路設計中的 PCB 控制器

PCB 控制器是 現代電子產品 的關鍵元件,常見於印刷電路板(PCB)上。這些控制器如同電子系統的大腦,負責處理資料、穩定電壓,並確保電路板上所有零件能順暢通訊。隨著電腦設計日益複雜,其重要性不言而喻。PCB 控制器種類繁多,應用各異,本文將深入探討如何挑選最合適的控制器,並將其整合進電子電路中。 1. 什麼是 PCB 控制器? PCB 控制器是一種積體電路(IC),負責管理整個印刷電路板的運作。它通常扮演板上的主處理器,向通訊模組、感測器或致動器等元件發送資料與指令。PCB 控制器會調控電壓、處理輸入與輸出資料,並監管時序活動,以確保電路板正常運作。 消費性裝置、工業機械與汽車系統皆因其體積小、效率高而採用 PCB 控制器。這些控制器對於電子產品的正常運行至關重要。 2. PCB 控制器的類型 市面上有多種 PCB 處理器,專為不同任務而設計。以下為電子設計中最常見的幾種: ⦁ 微控制器單元(MCU): 微控制器單元是專門用來控制電子設備特定功能的小型獨立 IC,通常在同一晶片上整合記憶體、處理核心與 I/O 埠。在家電、汽車電子與醫療設備等嵌入式系統中,MCU 負責讀取感測器資料並驅動馬達等任......