小型外觀積體電路(SOIC):封裝、規格與應用

2 分鐘

- 什麼是SOIC封裝?

- 小型外觀積體電路(SOIC)封裝規格

- SOIC封裝在電子產品中的常見應用

- SOIC封裝與其他IC封裝的比較

- SOIC PCB焊盤設計與DFM指南

- SOIC SMT組裝流程與常見缺陷

- 結論

- 關於SOIC封裝的常見問題

隨著設計從傳統的穿孔元件過渡到高密度的表面貼裝技術(SMT),小型外觀積體電路(SOIC)仍然是運算放大器、快閃記憶體、感測器和微控制器的產業標準。它證明了平衡工程的價值,在現代消費性電子產品所需的微型化與工業應用所需的堅固性之間提供了完美的妥協。

本文作為SOIC封裝的權威工程資源。我們將拆解圍繞本體寬度變化的困惑,分析驅動焊盤設計的具體機械尺寸。除了幾何形狀之外,我們還將檢視決定功率處理能力的熱特性以及引線框架結構背後的材料科學。

最後,我們將彌合設計與製造之間的差距,詳細說明特定的SMT組裝參數——從鋼網開口設計到回流曲線——以實現高良率的生產,並搭配JLCPCB的先進組裝能力。

什麼是SOIC封裝?

從技術上定義,SOIC封裝,即小型外觀積體電路,是一種表面貼裝積體電路(IC)封裝,其特徵是兩排平行的鷗翼形引線。它在佔位面積上大幅減少。

與等效的DIP封裝相比,SOIC通常可減少約30%–60%的PCB面積,具體取決於引腳數量和間距。

SOIC代表了組裝的「甜蜜點」。SOIC被廣泛使用,因為它在密度、可製造性和可重工性之間取得了平衡。

SOIC的鷗翼形引線提供了機械順應性和可見的焊點,使其在許多生產環境中對PCB翹曲和重工的容忍度比QFN更高。

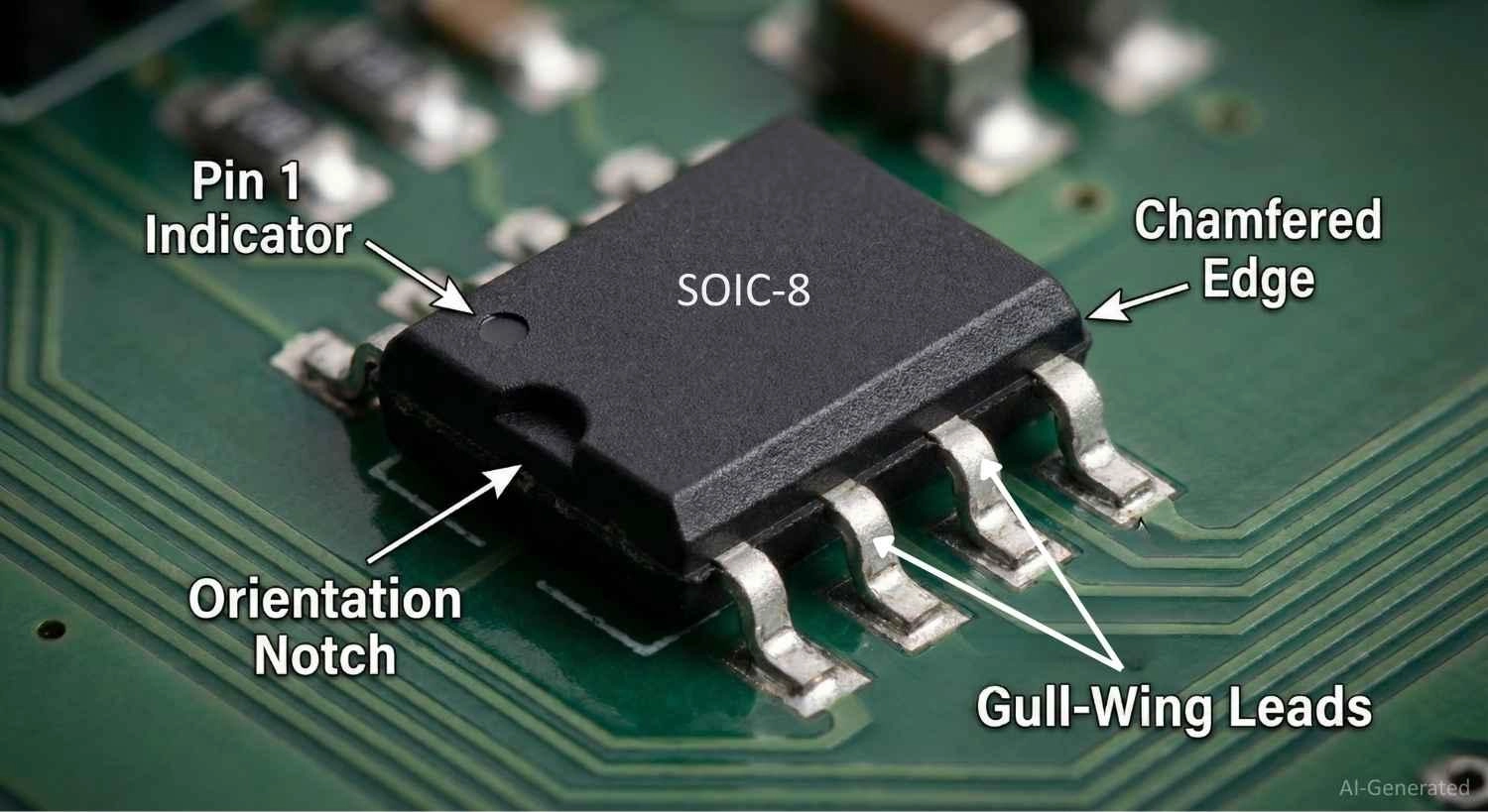

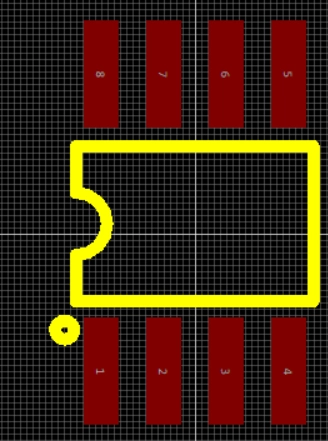

一顆小型外觀積體電路(SOIC)晶片安裝在印刷電路板上,顯示鷗翼形引線和引腳配置。

小型外觀積體電路(SOIC)封裝規格

了解SOIC的精確物理屬性對於PCB佈局和組裝至關重要。與通用描述不同,技術分析揭示了決定SMT鋼網設計和熱性能的具體尺寸。

| 封裝類型 | 本體寬度(mm) | 間距(mm) | 熱阻(𝜃JA) |

|---|---|---|---|

| 窄體 | 3.90mm(150 mil) | 1.27mm | ~100–120 °C/W |

| 寬體 | 7.50mm(300 mil) | 1.27mm | ~70–80 °C/W |

注意: θJA 強烈依賴於PCB銅箔和氣流,但典型的SOIC θJA 範圍約為 ~70 至 120 °C/W。

SOIC封裝尺寸與本體變化

SOIC封裝主要按其本體寬度分類。設計人員必須區分這些類型,以防止在CAD佈局中出現焊罩定義與非焊罩定義焊盤錯誤。

1. 窄體SOIC:

○ 本體寬度: 3.90mm(約150 mils)。

○ 典型引腳數: 8、14 和 16 引腳。

○ 用途: 標準邏輯閘、運算放大器和計時器。

2. 寬體SOIC:

○ 本體寬度: 7.50mm(約300 mils)。

○ 典型引腳數: 16、20、24 和 28 引腳。

○ 用途: 介面IC、較大的微控制器和需要更大晶片黏貼墊的記憶體晶片。

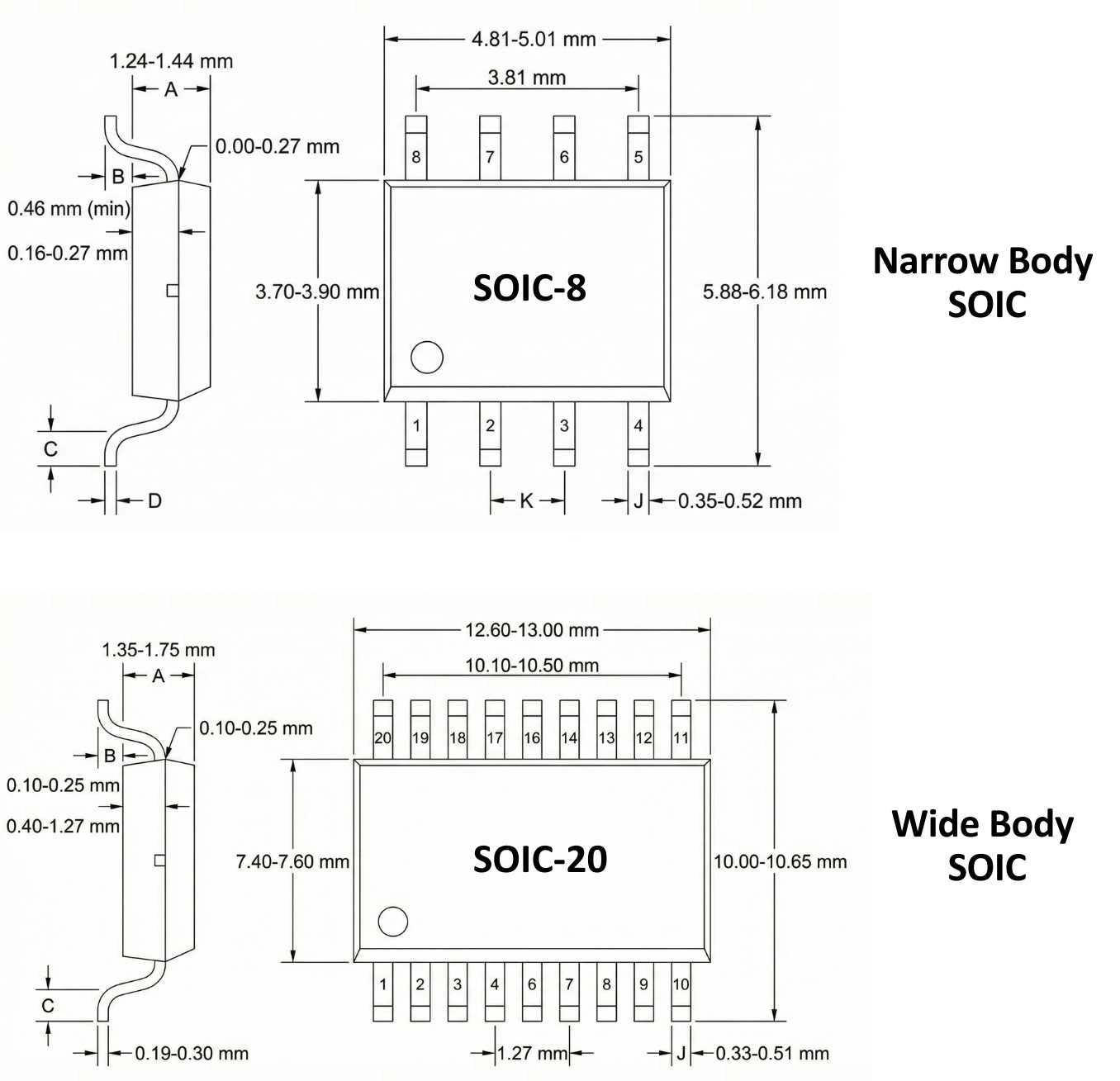

比較JEDEC窄體(SOIC-8)和寬體(SOIC-20)小型外觀積體電路封裝,顯示引腳間距和尺寸。

SOIC封裝引線幾何形狀、間距與共面性

SOIC的定義特徵是其1.27mm(50 mil)引腳間距。與細間距(FP)元件如SSOP(0.65mm)不同,1.27mm間距在焊膏印刷過程中允許更寬的製程窗口,顯著降低焊橋風險。

鷗翼形機構: SOIC的引線呈「鷗翼」形狀。從機械上講,這種形狀提供了順應性。在運作過程中,矽晶片、塑膠封裝和FR-4 PCB基板由於熱膨脹係數(CTE)不同而以不同的速率膨脹。

鷗翼形引線提供了機械順應性,可減少熱循環期間對焊點的應力傳遞,提高可靠性。

這對於汽車和工業PCB來說是一個關鍵的可靠性因素。

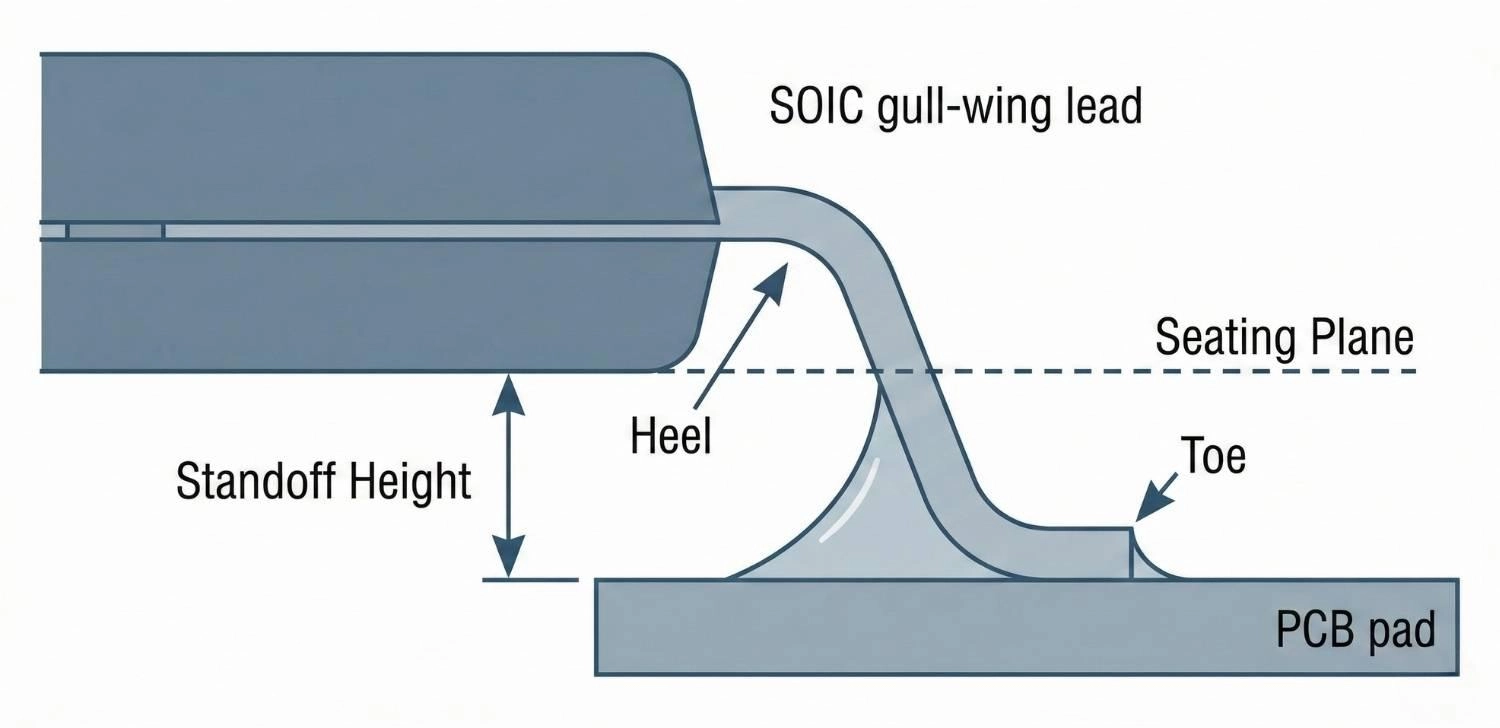

SOIC鷗翼形引線的側視圖,顯示腳跟、腳趾和在PCB焊盤上的焊點形成。

引線共面性: 為了可靠的SMT組裝,引線共面性——最高和最低引線之間的垂直距離——必須保持在0.10mm(4 mils)以內。超出此公差的偏差通常會在回流過程中導致「開路」焊點,因為引線無法接觸到印刷的焊膏。

SOIC封裝材料、引線框架與電鍍

● 引線框架: 引線框架通常由銅合金(例如Alloy 42、194、172)製成,具體取決於製造商和熱要求。

通常由銅合金194(CuFe2.3P)製成,以最大化熱導率(~260 W/m·K),促進從晶片到PCB的熱傳遞。

● 電鍍: 引線鍍有霧錫(Sn)或鎳-鈀-金(NiPdAu)。這種電鍍確保了在JLCPCB PCB組裝過程中的可焊性,並防止儲存期間氧化。

SOIC SMT包裝與處理注意事項

對於自動化組裝,SOIC元件以捲帶或塑膠管包裝供應。

● 捲帶: 大量SMT生產的首選。元件放置在壓紋口袋中,載帶密封覆蓋帶,允許快速送入貼片機。

● 塑膠管: 常用於小批量或原型製作,但需要管式送料器,載入速度可能較慢。

SOIC封裝在電子產品中的常見應用

小型外觀積體電路用途廣泛,幾乎應用於電子產業的每個領域。它在尺寸和手動重工性之間的平衡使其在BGA過於複雜而無法佈線或測試,但DIP又過於笨重的情況下特別受歡迎。

| 產業領域 | 應用情境 | 為何偏好SOIC | 常見範例 |

|---|---|---|---|

| 醫療設備 | 可攜式病患監護器、脈搏血氧儀 | 可靠的焊點可承受跌落/振動;尺寸比DIP更適合手持外殼。 | 精密運算放大器(如OPA系列)、ADC |

| 電信 | 路由器、數據機、基地台 | 由於引線短,高頻性能優異;收發器的標準封裝。 | RS-485收發器(MAX485)、線路驅動器 |

| 開發板 | Arduino複製板、ESP32擴展板、DIY套件 | 業餘愛好者和學生可手焊;比QFN更容易探測除錯。 | USB轉UART橋接器(CH340、CP2102)、穩壓器 |

| 汽車 | ECU(引擎控制單元)、儀表板控制器 | 對熱循環的高容忍度(鷗翼形應力釋放);AEC-Q100認證零件經常使用SOIC封裝。 | CAN匯流排收發器(TJA1050)、電壓穩壓器 |

| 穿戴式技術 | 智慧手錶(舊世代)、健康追蹤器 | 用於電源管理,其中超小型化(CSP)並非嚴格要求,但z軸高度很重要。 | 串列快閃記憶體(SPI Flash)、EEPROM |

| 工業自動化 | PLC輸入、馬達驅動器 | 抗工廠振動的穩健性;易於現場更換/維修。 | 閘極驅動器、隔離器、固態繼電器 |

SOIC封裝與其他IC封裝的比較

選擇正確的封裝是在電氣性能、熱管理和組裝良率之間的權衡。

SOIC與DIP(雙列直插封裝):通孔與SMT

雖然DIP更易於麵包板實驗,但電氣性能較差。DIP封裝的長引線會引入顯著的寄生電感(L)和電容(C)。

● 訊號完整性: SOIC較短的引線可最大限度地減少寄生電感,從而實現更快的開關速度和更高頻率的運作(>100 MHz),且訊號衰減較少。

● 熱路徑: SOIC平貼在PCB表面。晶片產生的熱量通過引線到銅箔的路徑更短($R_{\theta JL}$ 更低),從而改善散熱。

SOIC與SOP(小型外觀封裝):理解JEDEC與EIAJ的差異

一個常見的技術陷阱是將SOIC與SOP(小型外觀封裝)混淆,後者通常由EIAJ/JEITA規範定義。

● 差異: EIAJ SOP封裝的本體寬度通常為5.3mm——比窄體SOIC(3.9mm)寬,但比寬體SOIC(7.5mm)窄。

● 風險: 為EIAJ SOP元件放置標準SOIC焊盤通常會導致引線僅勉強觸碰焊盤,從而產生虛焊或開路接點。

● 解決方案: 使用JLCPCB零件庫時,務必交叉參考資料手冊中的具體本體寬度參數。

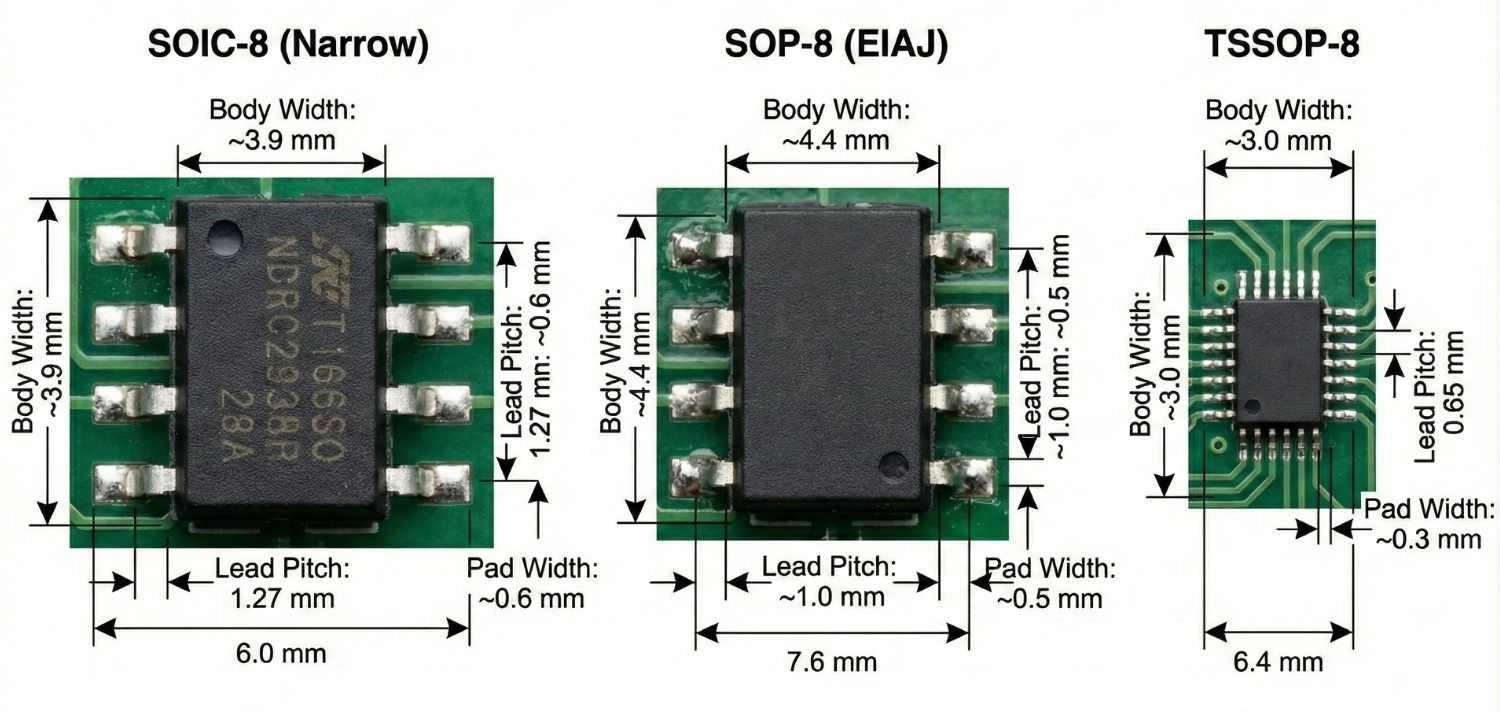

比較JEDEC SOIC、EIAJ SOP和TSSOP封裝的焊盤,以突顯尺寸差異和焊盤間距。

SOIC與TSSOP和QFN:尺寸、密度與穩健性

● TSSOP(薄型縮小型外觀封裝): 具有更薄的輪廓(最大1.1mm)和更緊密的間距(0.65mm)。雖然節省空間,但更容易發生焊橋,需要更薄的鋼網。

● QFN(四方扁平無引腳): 由於直接散熱焊盤,提供卓越的熱性能,但難以製作原型和檢查。SOIC允許在無需X光的情況下目視檢查焊點,簡化了品質控制(QC)。

SOIC PCB焊盤設計與DFM指南

為了確保在JLCPCB實現零缺陷製造,您的PCB佈局必須遵守嚴格的製造設計(DFM)指南。實體焊盤圖案決定了沉積的焊膏量。

SOIC焊盤圖案與焊盤設計要求

焊盤圖案幾何形狀決定了焊點的形成。

● 腳趾焊點(外側): 焊盤必須超出引線端0.35mm-0.55mm。這允許形成可見的焊料彎月面,對於自動光學檢測(AOI)驗證接點至關重要。

● 腳跟焊點(內側): 對於機械強度最關鍵的接點。焊盤應充分向內延伸,以允許焊料潤濕引線的「膝蓋」。

● 焊罩壩: 確保焊盤之間至少有0.1mm(4 mils)的焊罩網,以防止焊橋,儘管1.27mm的寬間距使其易於實現。

符合IPC-7351的SOIC-8 PCB焊盤圖案。

SOIC與SOIC-EP封裝的熱管理

高功率IC通常使用SOIC-EP(裸露焊盤)變體,其在底部包含一個散熱片。

● 焊盤內導通孔策略: 在中心接地焊盤上放置一組0.3mm的散熱導通孔。這些應縫合到內部接地層以散熱。

● 鋼網開口: 不要為裸露焊盤使用100%的開口。使用「窗格」設計(50-80%覆蓋率)以防止過多的焊料抬起,這可能導致封裝浮起並斷開訊號引腳。

專業提示: 使用EasyEDA或從JLCPCB零件庫直接下載經驗證的焊盤,以最小化幾何錯誤。

SOIC SMT組裝流程與常見缺陷

JLCPCBSMT組裝服務採用精密貼片機,但了解流程有助於設計出穩固的電路板。

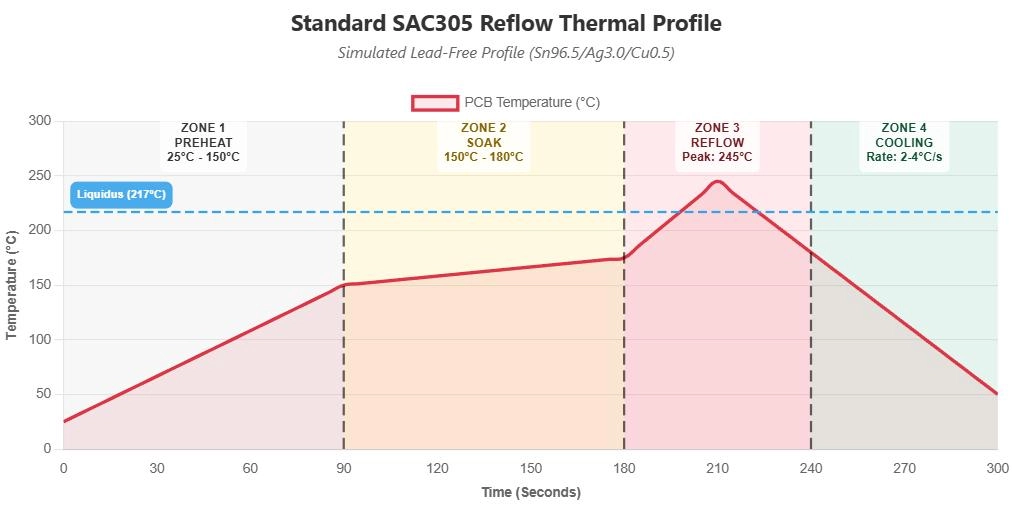

SOIC封裝的回流焊接曲線

1. 浸潤區(150°C–200°C): 60–120秒。活化助焊劑並確保塑膠本體和內部晶片達到熱平衡,以防止翹曲。

2. 回流區: 峰值溫度:對於SAC305,通常為235–245°C,不超過JEDEC最高260°C。”

3. 冷卻: 冷卻速率<4°C/s,以確保細晶粒焊料結構且無熱衝擊。

SMT回流焊接溫度曲線圖,顯示無鉛SAC305組裝的預熱、浸潤、峰值回流和冷卻區。

SOIC封裝的濕度敏感等級(MSL)與儲存

SOIC封裝具有吸濕性。如果濕氣在回流過程中被困在塑膠封裝內,它會膨脹成蒸汽,導致「爆米花」現象(封裝開裂)。

協議: 高MSL元件(等級3+)在暴露時間超過時,會在組裝前進行烘烤,遵循嚴格控制的儲存程序。

SOIC組裝缺陷與預防策略

● 焊橋: 在1.27mm間距上很少見。如果發生,檢查鋼網厚度是否超過0.15mm。

● 引線抬起或潤濕不均: 確保對稱的熱釋放連接到與大銅箔相連的焊盤。回流期間的不平衡熱流會導致潤濕力不均,從而導致引線抬起或焊點形成不足。

● AOI驗證: 鷗翼形幾何形狀允許自上而下相機輕鬆驗證潤濕角度,使SOIC成為最可靠的檢測封裝之一。

結論

小型外觀積體電路(SOIC)仍然是電子產業的巨擘。其平衡的物理特性使其成為需要比DIP更高密度,但需要比QFN或BGA封裝更易於處理和更好穩健性的工程師的理想選擇。通過了解技術規格並優化您的PCB焊盤,您可以確保無縫製造。

準備好將您的設計付諸實現了嗎? 立即將您的Gerber檔案上傳到JLCPCB,以進行即時DFM分析和高精度JLCPCB SMT組裝。

關於SOIC封裝的常見問題

Q1. 標準SOIC-8封裝的典型熱阻(𝜃JA)是多少?

標準窄體SOIC-8在標準FR-4板上的結到環境熱阻($\theta_{JA}$)通常約為100°C/W至120°C/W。這意味著每耗散一瓦功率,結溫上升約100°C。對於功率應用,請使用SOIC-EP變體或確保PCB上有大量銅箔。

Q2. SOIC封裝可以承受波峰焊嗎?

可以,標準SOIC封裝可以承受波峰焊,前提是他們被黏在PCB的底部。然而,由於尾隨引線上焊橋的風險,回流焊接是現代JLCPCB SMT組裝的首選方法。

Q3. 為什麼有些資料手冊會指定「Power SOIC」?

「Power SOIC」通常指的是SOIC-EP(裸露焊盤)變體,或是一種特定的引線框架設計,其中多個引腳在內部與晶片黏貼墊融合(通常是GND引腳)以充當散熱片。這些需要特定的PCB佈局策略來散熱。

Q4. 我可以手焊SOIC封裝嗎?

當然可以。1.27mm間距被認為是「手焊友好」的。它足夠寬敞,可以使用細尖烙鐵,無需顯微鏡,使其成為在轉向JLCPCB SMT量產前原型製作的理想選擇。

Q5. 引線電鍍如何影響SOIC元件的保存期限?

鍍有霧錫的SOIC引線通常保存期限為1-2年,之後「錫鬚」或氧化會成為問題。NiPdAu(鎳-鈀-金)電鍍提供更長的保存期限和更好的抗氧化性,如果您為長期生產儲存零件,這一點至關重要。

持續學習

理解 PCB 控制器在電子設計中的角色

PCB 控制器是設計與建構電氣系統的重要元件。它負責控制印刷電路板(PCB)上各種機械零件的功能,並確保彼此之間能順暢通訊。從家用科技到工廠自動化,PCB 控制器都有廣泛應用。本文旨在探討 PCB 控制器的重要性,涵蓋其種類、用途,以及選擇與使用的最佳實踐。 1. 什麼是 PCB 控制器? PCB 控制器是一種電腦元件,用於控制 PCB 的運作與功能。它通常包含微控制器或微處理器,以及記憶體晶片、電源管理單元與介面連接器等支援硬體。PCB 控制器的主要任務是讀取訊號並執行指令,協調板上其他元件的動作。統一控制能讓電子系統更高效且可靠。 2. PCB 控制器的類型 PCB 控制器依任務與效能需求不同,分為多種類型。以下是最常見的幾種: ⦁ 微控制器型控制器:這類控制器內建處理器,專門執行固定工作。低功耗與高彈性使其廣泛應用於家電與遙控器等消費性裝置。 ⦁ FPGA 控制器:現場可程式化閘陣列(FPGA)可隨時改變邏輯與行為,特別適合航太與工業環境中的複雜任務。透過程式設計即可隨時執行特定功能。 ⦁ 數位訊號處理器(DSP):專為高速完成複雜數學運算而設計,常見於音訊與視訊處理設備,如音響系統與視訊監......

電容器入門:它們如何運作、功能與類型

電容器是 PCB(印刷電路板)設計中不可或缺的元件,從儲能、濾波到穩壓皆扮演關鍵角色。無論是設計簡單電路或複雜多層板,了解不同類型的電容器及其應用都至關重要。電容器的基本結構由兩片金屬板中間夾一層介電質組成,可分為固定與可變兩種類型。 電容是電機工程的核心概念,代表系統儲存電荷的能力。電容器儲存電荷的能力稱為電容,單位為法拉。與電阻相同,電容器可串聯或並聯,進而改變總電容值。目前已開發出多種電容器供電子電路使用。本文將全面探討電容器的工作原理、功能、計算方法及各類型。想深入了解電子與 PCB 設計,請參閱我們最新的 PCB 製造流程 指南。 什麼是電容器及其工作原理? 電容器是被動元件,以電場形式儲存與釋放電能,由兩片導電板中間以絕緣介電質隔開。施加電壓時,金屬板會儲存電荷,兩板所帶電荷互補。電容器在電路中功能多元,其端子由金屬板引出供外部連接。 電容器的基本原理在於分離並儲存電荷。當連接電源時: 電子從負極流向其中一板(負極板),同時等量電子從另一板(正極板)被排斥至正極。 此電荷分離在介電質內建立電場,電容器持續充電,直到兩板電壓等於外加電壓。 充飽後,電容器可充當臨時電池,將電能儲存至電路需......

電子電路設計中的 PCB 控制器

PCB 控制器是 現代電子產品 的關鍵元件,常見於印刷電路板(PCB)上。這些控制器如同電子系統的大腦,負責處理資料、穩定電壓,並確保電路板上所有零件能順暢通訊。隨著電腦設計日益複雜,其重要性不言而喻。PCB 控制器種類繁多,應用各異,本文將深入探討如何挑選最合適的控制器,並將其整合進電子電路中。 1. 什麼是 PCB 控制器? PCB 控制器是一種積體電路(IC),負責管理整個印刷電路板的運作。它通常扮演板上的主處理器,向通訊模組、感測器或致動器等元件發送資料與指令。PCB 控制器會調控電壓、處理輸入與輸出資料,並監管時序活動,以確保電路板正常運作。 消費性裝置、工業機械與汽車系統皆因其體積小、效率高而採用 PCB 控制器。這些控制器對於電子產品的正常運行至關重要。 2. PCB 控制器的類型 市面上有多種 PCB 處理器,專為不同任務而設計。以下為電子設計中最常見的幾種: ⦁ 微控制器單元(MCU): 微控制器單元是專門用來控制電子設備特定功能的小型獨立 IC,通常在同一晶片上整合記憶體、處理核心與 I/O 埠。在家電、汽車電子與醫療設備等嵌入式系統中,MCU 負責讀取感測器資料並驅動馬達等任......

PCB 板連接器:可靠連接的關鍵元件

PCB 板連接器是電子產品中的重要元件,因為它們讓不同電路元件之間能夠建立電氣連接。這些連接器確保資料與電力在系統中順暢流動,從消費性電子產品到重型機械都能見到它們的身影。本文將介紹 PCB 板連接器的類型、用途,以及選擇與佈局的最佳做法。 什麼是 PCB 板連接器? PCB 板連接器是一種電子元件,用來連接印刷電路板(PCB)上的不同部分,或將 PCB 與外部設備連接。它們讓設計更具彈性,便於組裝與維護。連接器有各種尺寸、形狀與功能,但其主要任務是建立穩固的電氣連接。 PCB 連接器的類型 PCB 連接器種類繁多,每種都針對特定用途與需求設計。以下是最常見的類型: 排針連接器: 這類連接器具有多支插針,通常焊接在 PCB 上,可方便地與其他元件或子板連接。 插座連接器: 插座連接器專為搭配排針而設計,可快速且安全地完成連接,常用於需要頻繁更換元件的場合。 穿孔式連接器: 穿孔連接器需要先在 PCB 上鑽孔再進行安裝,常見於高可靠性應用,能提供穩固的連接。 表面貼裝連接器: 這類連接器直接焊接在 PCB 表面,節省空間,適合現代電子產品的小型化設計。 PCB 板連接器在電路設計中的重要性 PCB ......

每塊 PCBA 上必備的元件

印刷電路板組裝(PCBA)是現代電子設備的核心,透過在電路板上連接多個電子元件,使各種系統能夠無縫運作。雖然 PCBA 的設計與複雜度會依應用而異,從消費性電子到工業系統都有,但某些核心元件幾乎在每塊組裝板上都會出現。隨著電路板元件多年來的演進,所有參與 PCB 設計、製造與組裝流程的人員,都必須更深入了解這些元件的特性。本文將介紹電路板組裝上常見的元件、其應用、功能,以及在電子設備中使用這些元件的重要性。 過去數十年電子技術的演進: 電路元件的歷史可追溯到 19 世紀末,當時的 PCB 使用電木、美耐板、紙板與薄木板等材料。被動元件如電阻、電容與電感於 19 世紀問世;20 世紀初真空管登場,不久後電晶體取代笨重的真空管。 接著積體電路技術徹底改變世界,1980 年代表面黏著技術(SMT)問世,進一步縮小電路板元件尺寸並簡化組裝流程。多年來元件的演進,使 PCB 在不損失電氣性能的前提下縮至微型化,並促成更高效、更強大的全球通用設備。想了解更多,請參考我們的 PCB 組裝流程完整指南。 各種元件的識別與數值: 視覺識別: 這是辨認電路板元件的第一步。透過觀察元件的尺寸、形狀、顏色與標記,通常就能......

PCB 保險絲:確保現代電子產品的電路保護

簡介 在電子領域中,PCB 保險絲是保護電路免於過電流與短路損壞的關鍵元件。隨著電子裝置日益複雜且精簡,有效的電路保護更顯重要。無論是表面黏著型(SMD)保險絲或插件式保險絲,PCB 保險絲在維持電路完整性與功能上都扮演核心角色。本文深入探討 PCB 保險絲的各種面向,包含類型、選用準則、安裝方式與應用,並強調其在現代 PCB 設計與組裝中的重要性。 認識 PCB 保險絲及其重要性 PCB 保險絲是一種可犧牲的元件,專門用來保護電氣電路免於過大電流。當發生過電流時,保險絲會「熔斷」或熔化,切斷電流並防止其他元件受損。這種簡單卻有效的機制確保了電氣安全,避免昂貴的維修或更換。從消費性電子到工業機械,所有電子裝置都需要電路保護,因此 PCB 保險絲不可或缺。 1. PCB 保險絲的類型 表面黏著型(SMD)保險絲: 這類保險絲適用於自動化 PCB 組裝流程,直接貼裝於 PCB 表面。SMD 保險絲體積小巧,適合高密度電路板,是現代電子產品的理想選擇。 插件式保險絲: 這類保險絲插入 PCB 上的鑽孔並在背面焊牢。插件式保險絲常用於需要高機械強度與耐用度的應用。 熱熔斷保險絲: 此類保險絲用於防止電路過......