QFP vs QFN:哪種 IC 封裝適合您的 PCB?

2 分鐘

- 什麼是 QFP 封裝?

- 什麼是 QFN 封裝?

- QFP vs QFN:快速選擇指南

- QFP vs QFN:關鍵差異一覽

- QFP vs QFN:應用情境—何時選哪種?

- QFP vs QFN:PCB 腳位與設計要點

- QFP vs QFN:焊接與組裝挑戰

- JLCPCB 如何支援您的 QFP 與 QFN 專案

- QFP 封裝優點

- QFP 封裝限制

- QFN 封裝優點

- QFN 封裝限制

- 常見問題

- 結論:如何選擇 QFP 與 QFN

QFP 與 QFN 是現代 PCB 設計中兩種廣泛使用的 IC 封裝,各自在尺寸、組裝與效能上提供不同優勢。在 QFP vs QFN 之間的選擇,將直接影響佈線複雜度、焊接可靠性、熱管理與製造成本。

封裝選擇不當可能導致生產良率低、重工率高,以及長期可靠性問題。本指南將從結構、PCB 腳位、組裝流程與典型應用等方面比較 QFP 與 QFN,協助工程師與設計師為專案做出明智決策。

什麼是 QFP 封裝?

QFP 為 Quad Flat Package 的縮寫,是一種表面黏著 IC 封裝,四邊延伸出鷗翼型引腳,可在維持可靠電氣與機械效能的同時支援中至高腳數。

憑藉成熟的製程與廣泛的產業支援,QFP 封裝廣泛應用於微控制器、介面晶片與嵌入式處理器。

典型腳數介於 44 至 200 腳以上,常見腳距為 0.8 mm、0.65 mm 與 0.5 mm。這些標準化尺寸使 QFP 元件與大多數 PCB 製造及組裝流程相容。

什麼是 QFN 封裝?

QFN 為 Quad Flat No-Lead 的縮寫,是一種表面黏著 IC 封裝,底部以扁平金屬焊墊取代延伸引腳。這些焊墊直接焊接於 PCB,使封裝尺寸與高度均小於傳統有引腳封裝。

多數 QFN 封裝亦具中央裸露散熱焊墊,可將晶片熱量傳導至 PCB。此結構改善熱與電氣效能,使 QFN 常見於高速與高功率應用。

典型 QFN 腳數介於 16 至 100 腳以上,常見腳距為 0.5 mm 或更小。憑藉小巧尺寸與優異電氣特性,QFN 封裝廣泛用於無線模組、電源管理 IC 與高頻裝置。

QFP vs QFN:快速選擇指南

若需快速在 QFP 與 QFN 間抉擇,下表匯總最實用的決策要素。

| 需求 | 建議封裝 | 原因 |

|---|---|---|

| 易重工與除錯 | QFP | 引腳可見,便於焊接與探測 |

| 縮小 PCB 尺寸 | QFN | 無外部引腳,佔位更小 |

| 高頻效能 | QFN | 寄生參數低,訊號路徑短 |

| 快速打樣 | QFP | 手焊與修改容易 |

| 大量生產 | QFN | 更適合自動化組裝 |

| 熱效能 | QFN | 裸露焊墊提升散熱 |

| 目視檢查 | QFP | 焊點易於檢視 |

工程師提示:若設計仍在驗證或迭代階段,先採用 QFP 可大幅縮短開發時程;待設計成熟穩定後,再轉換至 QFN,通常是縮小尺寸與提升效能的最佳途徑。

QFP vs QFN:關鍵差異一覽

選擇 QFP 或 QFN 前,需先了解兩者在結構、電氣與製造上的差異。雖然兩者皆廣泛使用,但各自滿足不同應用需求。

下表摘要 QFP 與 QFN 的主要差異。

QFP vs QFN 比較表

| 特性 | QFP(Quad Flat Package) | QFN(Quad Flat No-Lead) |

|---|---|---|

| 引腳型態 | 鷗翼型引腳 | 底部焊墊(無引腳) |

| PCB 佔位 | 較大 | 較小 |

| 腳位密度 | 中等 | 高 |

| 組裝難度 | 較低 | 較高 |

| 熱效能 | 中等 | 較佳 |

| 檢測方式 | 目視 / AOI | X-ray / 高階 AOI |

| 重工性 | 容易 | 困難 |

| 訊號完整性 | 良好 | 更佳 |

| 製造良率 | 穩定 | 視製程而定 |

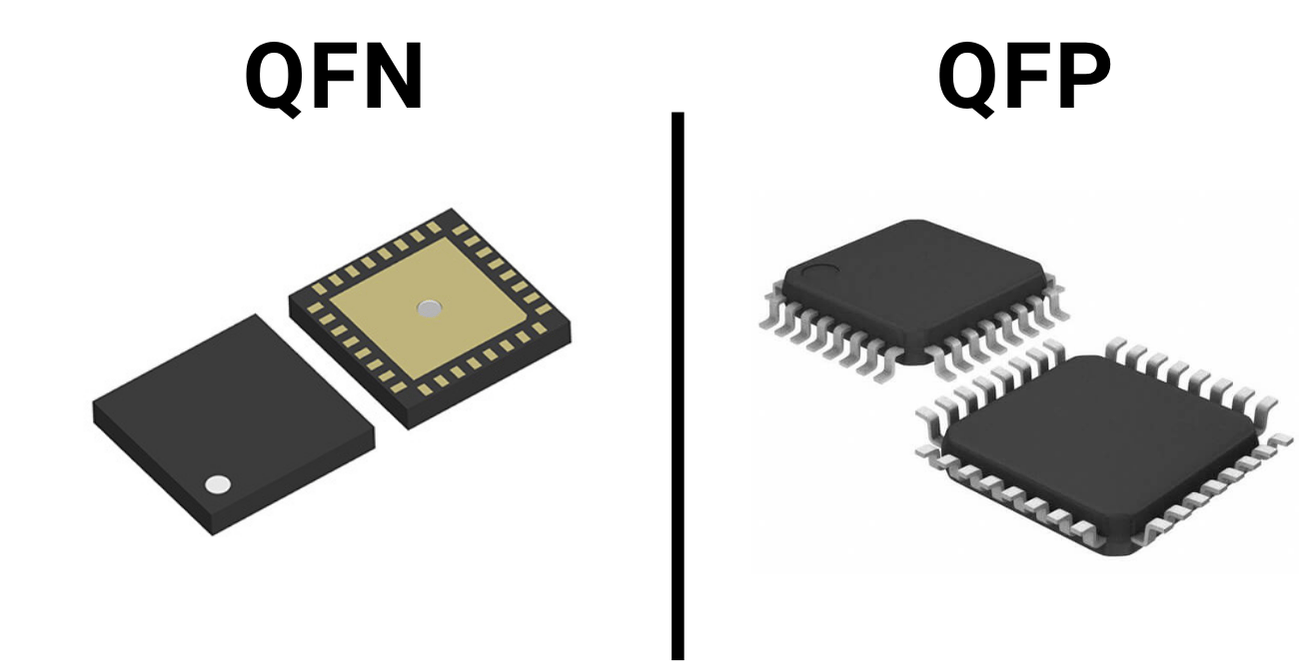

1. QFP vs QFN:結構差異

兩者主要差異在於引腳結構。

QFP 結構

● 使用外部鷗翼型引腳

● 引腳自四邊延伸

● 焊點可見且可接觸

● 易於檢查與重工

QFN 結構

● 使用底部焊墊,無外部引腳

● 焊墊位於封裝下方

● 封裝尺寸更小

● 電氣效能更佳

● 檢查與重工難度較高

重點:QFP 著重可觸及與易維修,QFN 著重小型化與高效能。

2. QFP vs QFN:對 PCB 佈線的影響

封裝選擇直接影響 PCB 走線複雜度。

QFP 佈線特性

● 需較多板面空間

● 佔位面積大

● 扇出走線容易

● 適用於少層板

QFN 佈線特性

● 可實現緊湊設計

● 需精準焊墊布局

● 需留意貫孔與散熱焊墊設計

● 佈線缺陷風險較高

常見風險:QFN 走線不當可能導致焊接失效與熱問題。

設計提示:簡單佈線選 QFP,空間受限且 DFM 資源充足時選 QFN。

3. QFP vs QFN:熱與電氣效能比較

熱與電氣行為是主要決策因素。

熱效能

QFN

● 中央裸露散熱焊墊

● 熱傳導效率高

● 接面溫度更低

● 更適合功率元件

QFP

● 無中央散熱焊墊

● 散熱能力中等

● 熱阻較高

電氣效能

QFN

● 訊號路徑短

● 寄生電感低

● 更適合高頻電路

QFP

● 引腳較長

● 寄生效應較高

● 較不適合超高速設計

重點:QFN 在熱與高速應用更勝一籌。

4. QFP vs QFN:製造與成本考量

製造複雜度直接影響成本與良率。

QFP 製造特點

● 組裝製程成熟

● 目視檢查容易

● 良率高且穩定

● 重工成本低

● 適合原型與小批量

QFN 製造特點

● 需精準鋼板設計

● 需高精度貼裝

● 對回焊曲線敏感

● 常需 X-ray 檢查

● 製程控管要求更高

成本觀點

| 生產類型 | 建議封裝 |

|---|---|

| 原型製作 | QFP |

| 低至中量產 | QFP |

| 大量生產(先進產線) | QFN |

成本提示:QFN 在大量生產時具成本優勢,但早期專案仍以 QFP 較保險。

QFP vs QFN:應用情境—何時選哪種?

兩者雖皆跨產業通用,但結構差異使其更適合特定應用。下表摘要典型使用情境:

| 應用領域 | QFP(Quad Flat Package) | QFN(Quad Flat No-Lead) |

|---|---|---|

| 微控制器(MCU) | 常見,易重工 | 較少見,偏好精簡設計 |

| DSP 與通訊 IC | 適合原型 | 高頻或精簡模組 |

| 消費性電子 | 中等密度板 | 手機、穿戴等空間受限裝置 |

| 工業控制 | 穩定、易檢查 | 精簡且需散熱之板 |

| 電源管理 IC | 散熱中等 | 熱效能優異 |

| 嵌入式系統 | 原型與小量 | 高密度、效能導向設計 |

重點:

● QFP 適合重視檢查、重工與打樣的專案。

● QFN 適合空間受限、高效能且需精準焊接與散熱的板。

QFP vs QFN:PCB 腳位與設計要點

正確的腳位設計對兩種封裝的可靠焊接與量產穩定度至關重要。

QFP 腳位指引

● 採用標準 IPC 焊墊圖形

● 確保綠漆開口足夠

● 預留探針與重工空間

● 維持焊墊等距,避免橋接

適用:初學者、原型與低風險設計

QFN 腳位指引

● 精準設計焊墊與散熱焊墊尺寸

● 最佳化鋼板開孔比例

● 考慮 via-in-pad 強化散熱

● 平衡熱與電氣效能

適用:精簡且高效能板

常見 PCB 設計錯誤

● 焊墊尺寸過大或過小

● QFN 散熱焊墊連接不良

● 焊膏覆蓋不當

● 忽略原廠焊墊圖形資料

設計提示:製板前務必以 DFM 檢查腳位,降低組裝缺陷並提升良率。

QFP vs QFN:焊接與組裝挑戰

焊接是選擇 QFP 或 QFN 的關鍵,因各自難點將影響良率與可靠度。

QFP 焊接提示

● 使用適當回焊曲線,避免冷焊

● 鷗翼引腳可目視檢查與補焊

● 立碑少見,因引腳可見

● 適合原型與中小批量

主要優勢:相較於無引腳封裝,檢查與重工更容易

QFN 焊接提示

● 精準設計鋼板,兼顧散熱與訊號焊墊

● 控制回焊曲線,避免空洞

● 焊點位於底部,需 X-ray 或高階 AOI

● 貼裝與焊膏量精度要求更高

主要挑戰:檢查與重工困難,但能實現更小佔位與更佳熱/電效能

兩者通用最佳實踐

● 依原廠規格驗證回焊溫度曲線

● 組裝前檢查焊墊對位與焊膏覆蓋

● QFN 考慮採用 AOI/X-ray

● 量產前先以原型驗證焊接製程

JLCPCB 如何支援您的 QFP 與 QFN 專案

將 QFP 或 QFN 設計付諸實現,選對製造商至關重要。

JLCPCB 提供 24–48 小時快速打樣,方便您測試與迭代——尤其適合需多次重工的 QFP 元件。

我們的先進 SMT 與PCBA 服務滿足 QFN 焊接精度需求,含 X-ray 與 AOI 檢查,確保每顆焊點可靠。

全球物流網路讓您快速收板,兼顧交期與品質。

QFP 封裝優點

1. 易於檢查與重工

QFP 外露引腳可透過 AOI 或人工目視輕鬆檢查,缺陷焊點可快速辨識與修復,適合原型與低至中量產。相較於無引腳封裝,重工與替換更簡單,降低維護成本與停機時間。

2. 製程標準化

QFP 封裝在腳位設計、焊接曲線與檢查方法上均有成熟產業標準。多數 PCB 製造與組裝廠經驗豐富,可確保穩定量產品質與一致良率,降低製造風險並縮短開發週期。

QFP 封裝限制

1. 佔位面積大

相較於現代小型封裝,QFP 因延伸引腳需更大 PCB 面積,限制其在穿戴與超小型模組等尺寸敏感產品的應用。

2. 腳位密度低

雖支援較高腳數,但 QFP 腳位密度仍低於 QFN 或 BGA。當腳距縮小,走線難度與橋接風險增加,影響良率,使其較不適合高密度高效能設計。

QFN 封裝優點

1. 更小佔位與更高腳位密度

無外部引腳使 QFN 佔用 PCB 面積遠小於 QFP,可在同尺寸板上放置更多元件,對 IoT、智慧型手機與可攜裝置的微型化設計尤為有利。

2. 更佳熱與電氣效能

底部裸露散熱焊墊提供高效熱傳導路徑,降低接面溫度並提升長期可靠度。同時,晶片至 PCB 的電氣路徑短,寄生電感與電阻更低,訊號完整性更佳,適合高速高頻電路。

QFN 封裝限制

1. 檢查與重工困難

QFN 焊點位於封裝底部,光學檢查受限,常需 X-ray 或高階 AOI 才能發現空洞、橋接或焊料不足。重工亦需專用設備與經驗豐富的技術員。

2. 對組裝精度要求高

QFN 需精準的焊膏印刷、貼裝與回焊曲線控制。鋼板或溫度設定不當易導致空洞、潤濕不良或黏著不足,因此製程控管與製造經驗要求較 QFP 更高。

常見問題

Q1:QFN 比 QFP 好嗎?

視設計需求而定。QFN 佔位小、腳位密度高、熱與電氣效能佳,適合精簡高速板;QFP 則易於檢查與重工,利於原型與低至中量產。

Q2:QFP 容易重工嗎?

是的。鷗翼引腳外露,可目視檢查、補焊與替換,是 QFP 仍受歡迎的主因之一。

Q3:QFN 需要 X-ray 檢查嗎?

通常需要。焊點位於底部,光學檢查困難,需 X-ray 或高階 AOI 確保品質,尤其對高可靠應用。

Q4:QFP 與 QFN 哪個便宜?

視產量與組裝複雜度而定。QFP 製程簡單,原型與小量成本較低;QFN 大量生產時具競爭力,但需更嚴格製程與檢查,可能增加組裝成本。

結論:如何選擇 QFP 與 QFN

選擇 QFP 或 QFN 取決於專案需求。QFP 適合需易檢查與重工的原型;QFN 則在精簡、高效能板中展現更優熱與電氣特性。

JLCPCB 同時支援 QFP 與 QFN 專案,提供快速打樣、精密 SMT、X-ray/AOI 檢查,確保焊接可靠與高品質量產。全球物流讓您無論小量原型或大量生產,都能快速交貨。選對封裝與製造商,讓您的 PCB 專案在效能、可靠度與時程上皆能高效達標。

持續學習

斷路器類型與應用完整指南

電路可能受損,導致可靠性降低。因此,電路需要使用保護裝置來保護。通常保險絲、扼流圈、去耦電容、齊納二極體、保護二極體就足以防止電子設備發生意外。斷路器在電氣系統中也用於相同目的。斷路器可定義為一種開關裝置,透過充當開關並中斷電流來防止電氣系統受損。本文將深入探討斷路器及其各種類型,研究其優缺點、運作原理等。 1. 什麼是斷路器? 斷路器是一種可手動或自動操作的開關機構,當偵測到電路中有異常電流或故障時,切斷電流,從而減少過載與短路情況。 斷路器與保險絲功能相同,但與保險絲不同,啟動或觸發時不會被破壞/燒毀。與保險絲不同,我們無需更換,只需在確認故障後重新設定即可。發生過載時,斷路器會開啟電路以防止任何損害。它們配有開關,可在跳脫後恢復閉合位置。斷路器廣泛用於家庭、工業和商業電氣設置,以保護設備免受損壞。 2. 如何選擇斷路器: 選擇斷路器時,需了解其規格。主要考量因素包括: 額定電壓:額定電壓是斷路器兩端可施加的最大電壓。需了解目標應用所需的電壓,並選擇電壓容量足以應對的斷路器。 連續電流額定值:要了解連續電流額定值,需確認安培數。安培額定值表示斷路器在不過熱的情況下可承受的連續電流。 頻率:要確......

微處理器與積體電路:主要差異、類型與應用

在電子領域中,一切源自矽,今天我們將討論兩種不同的矽晶片。這不是一場戰鬥,而是一場性價比的競賽。積體電路是一種半導體晶片,內部容納了數千到數十億個電晶體。積體電路將 MOS 電晶體的基本結構整合在一小片矽晶圓上。這些 MOS 電晶體以特定方式連接,實現了與更大電路相同的功能。這些 MOS 電晶體僅用於實現特定功能,無法被程式化,僅在電路連接時執行操作。然而,透過改變外部電路,單一積體電路可實現多種功能。 另一方面,微處理器是一個包含 CPU 及多個子 IC 的完整系統,可依指令進行程式化。在接下來的段落中,我們將深入探討。積體電路的起源可追溯至 1960 年代,將電路縮小至拇指大小的想法廣受歡迎,因為它能節省成本與空間,並改變多年來電子設計的方式。在本部落格中,我們將: 了解什麼是積體電路。 了解什麼是微處理器。 探討使用微處理器與積體電路設計時的挑戰。 1. 什麼是積體電路? 積體電路(有時稱為晶片或微晶片)是一種半導體晶圓,通常由矽製成,整合了包括電阻、電晶體、電容和二極體在內的電子電路,這些元件相互連接以執行特定功能。在積體電路出現之前,電晶體和電阻等元件需在電路板上焊接連接。隨著積體電路的......

什麼是電源管理 IC(PMIC):功能與應用

電源管理 IC(PMIC)是一種專門設計用來管理主機系統電源需求的積體電路。它能有效率地為裝置內的各種元件(如處理器、記憶體單元與周邊設備)分配、調節、轉換與監控電力。隨著對小型化、電池供電且高效能裝置的需求持續成長,PMIC 已成為跨產業系統設計中不可或缺的一環。嵌入式與應用處理器,以及其他複雜系統中的元件,都需要多組電源軌與多個電源域。請從這裡查看完整的 PCB 製造 流程。 在這類系統中使用離散元件進行電源管理成本高昂。將多組穩壓器與控制電路整合至單一晶片的電源管理積體電路(PMIC),是實現完整電源供應解決方案的理想選擇。它們可減少元件數量與電路板空間,同時以簡單且具成本效益的方式管理系統電源。本文將探討 PMIC 的定義、核心功能,以及其在現代電子領域的廣泛應用。 PMIC 如何運作? 半導體業界有時將 PMIC 類比為人體的「心臟」,「泵送」血液至各器官,使其維持功能。PMIC 扮演「電壓轉換器」的角色,將電池或電源端的電壓進行轉換,調整、協調並分配適當的電壓給電路中的每個元件。 PMIC 負責電源系統的電壓時序控制,為各種負載供電,並提供過壓、欠壓、過電流或其他熱問題的保護。因此,P......

理解 PCB 控制器在電子設計中的角色

PCB 控制器是設計與建構電氣系統的重要元件。它負責控制印刷電路板(PCB)上各種機械零件的功能,並確保彼此之間能順暢通訊。從家用科技到工廠自動化,PCB 控制器都有廣泛應用。本文旨在探討 PCB 控制器的重要性,涵蓋其種類、用途,以及選擇與使用的最佳實踐。 1. 什麼是 PCB 控制器? PCB 控制器是一種電腦元件,用於控制 PCB 的運作與功能。它通常包含微控制器或微處理器,以及記憶體晶片、電源管理單元與介面連接器等支援硬體。PCB 控制器的主要任務是讀取訊號並執行指令,協調板上其他元件的動作。統一控制能讓電子系統更高效且可靠。 2. PCB 控制器的類型 PCB 控制器依任務與效能需求不同,分為多種類型。以下是最常見的幾種: ⦁ 微控制器型控制器:這類控制器內建處理器,專門執行固定工作。低功耗與高彈性使其廣泛應用於家電與遙控器等消費性裝置。 ⦁ FPGA 控制器:現場可程式化閘陣列(FPGA)可隨時改變邏輯與行為,特別適合航太與工業環境中的複雜任務。透過程式設計即可隨時執行特定功能。 ⦁ 數位訊號處理器(DSP):專為高速完成複雜數學運算而設計,常見於音訊與視訊處理設備,如音響系統與視訊監......

電容器入門:它們如何運作、功能與類型

電容器是 PCB(印刷電路板)設計中不可或缺的元件,從儲能、濾波到穩壓皆扮演關鍵角色。無論是設計簡單電路或複雜多層板,了解不同類型的電容器及其應用都至關重要。電容器的基本結構由兩片金屬板中間夾一層介電質組成,可分為固定與可變兩種類型。 電容是電機工程的核心概念,代表系統儲存電荷的能力。電容器儲存電荷的能力稱為電容,單位為法拉。與電阻相同,電容器可串聯或並聯,進而改變總電容值。目前已開發出多種電容器供電子電路使用。本文將全面探討電容器的工作原理、功能、計算方法及各類型。想深入了解電子與 PCB 設計,請參閱我們最新的 PCB 製造流程 指南。 什麼是電容器及其工作原理? 電容器是被動元件,以電場形式儲存與釋放電能,由兩片導電板中間以絕緣介電質隔開。施加電壓時,金屬板會儲存電荷,兩板所帶電荷互補。電容器在電路中功能多元,其端子由金屬板引出供外部連接。 電容器的基本原理在於分離並儲存電荷。當連接電源時: 電子從負極流向其中一板(負極板),同時等量電子從另一板(正極板)被排斥至正極。 此電荷分離在介電質內建立電場,電容器持續充電,直到兩板電壓等於外加電壓。 充飽後,電容器可充當臨時電池,將電能儲存至電路需......

電子電路設計中的 PCB 控制器

PCB 控制器是 現代電子產品 的關鍵元件,常見於印刷電路板(PCB)上。這些控制器如同電子系統的大腦,負責處理資料、穩定電壓,並確保電路板上所有零件能順暢通訊。隨著電腦設計日益複雜,其重要性不言而喻。PCB 控制器種類繁多,應用各異,本文將深入探討如何挑選最合適的控制器,並將其整合進電子電路中。 1. 什麼是 PCB 控制器? PCB 控制器是一種積體電路(IC),負責管理整個印刷電路板的運作。它通常扮演板上的主處理器,向通訊模組、感測器或致動器等元件發送資料與指令。PCB 控制器會調控電壓、處理輸入與輸出資料,並監管時序活動,以確保電路板正常運作。 消費性裝置、工業機械與汽車系統皆因其體積小、效率高而採用 PCB 控制器。這些控制器對於電子產品的正常運行至關重要。 2. PCB 控制器的類型 市面上有多種 PCB 處理器,專為不同任務而設計。以下為電子設計中最常見的幾種: ⦁ 微控制器單元(MCU): 微控制器單元是專門用來控制電子設備特定功能的小型獨立 IC,通常在同一晶片上整合記憶體、處理核心與 I/O 埠。在家電、汽車電子與醫療設備等嵌入式系統中,MCU 負責讀取感測器資料並驅動馬達等任......