PCB 層數解析:透過智慧疊構、標準與設計實踐打造更優質的電路板

1 分鐘

- 規劃有效的 PCB 層疊構造

- 遵守 PCB 層的標準與規範

- 進階 PCB 層設計技巧

- 常見 PCB 層問題與排除

- 常見問題(FAQ)

PCB 是由銅箔與絕緣層層疊而成的「三明治」,用來形成電路板。每一層都有特定功能:有些負責承載訊號(連接元件的走線),有些則作為完整的電源或接地平面。可以把 PCB 層想像成大樓的樓層,每層扮演不同角色,例如一層是辦公室(訊號),另一層是倉庫(接地/電源)。層數依設計複雜度而定,從單層到十幾層的高階電子產品都有。本文將說明如何有效安排這些層,降低 EMI 並提升訊號完整性,關鍵就在於佈線與配置的規劃。

單層與多層 PCB 的定義

最基礎的是單層 PCB,只有一面銅箔,製造成本低,適合 LED 驅動等低成本電路。

業界主流是雙層 PCB,上下兩面都有銅箔,走線選擇翻倍,兩層間透過稱為「過孔」的小孔互連訊號。

多層 PCB則使用三層以上銅箔,內部通常夾有電源與接地平面,並位於訊號層之間。手機、筆電、醫療設備等高密度產品都採用多層板,以滿足嚴格的雜訊管理需求。

從簡單到複雜的層配置演進

早期電子產品單雙層板即可應付,但隨著功能複雜與速度提升,設計者必須增加層數。每多一層就多出佈線空間,避免交叉。實際應用上,低階產品為成本考量維持 2–4 層;中階設計常見 6 層;高速高階系統則普遍 8 層以上。8 層板被視為「高速/高密度設計的最佳選擇」,多重平面配對提供優異的 EMI 抑制與電源穩定性。

規劃有效的 PCB 層疊構造

層疊(stackup)就是從上到下所有銅層與絕緣層的順序。開始拉線前就得把層疊敲定,因為 4、6、8 層板並非每層都能隨意走線;亂選層會導致嚴重訊號完整性問題。聰明的疊層能為電流提供清晰的迴路,並為高速線控制阻抗。

訊號層、電源層與接地層的策略配置

接地與電源平面(去耦配對):把完整的接地與電源平面放在疊層中段並相鄰,兩者就像內建電容,提供優秀的去耦效果,降低迴路電感與系統雜訊。連續的接地平面緊貼訊號層,可為迴流電流提供短而低電感的路徑。高速線盡量避免跨過平面分割,若非得跨越,可用縫合過孔橋接迴路。

訊號層擺放:最關鍵的訊號應緊鄰參考平面。永遠在訊號走線下方放置完整接地平面,以維持訊號完整性並降低 EMI。例如 4 層板常見安排:

- Top = 訊號

- Layer 2 = 接地

- Layer 3 = 電源

- Bottom = 訊號

如此每個外層訊號都緊耦合到平面,阻抗穩定。

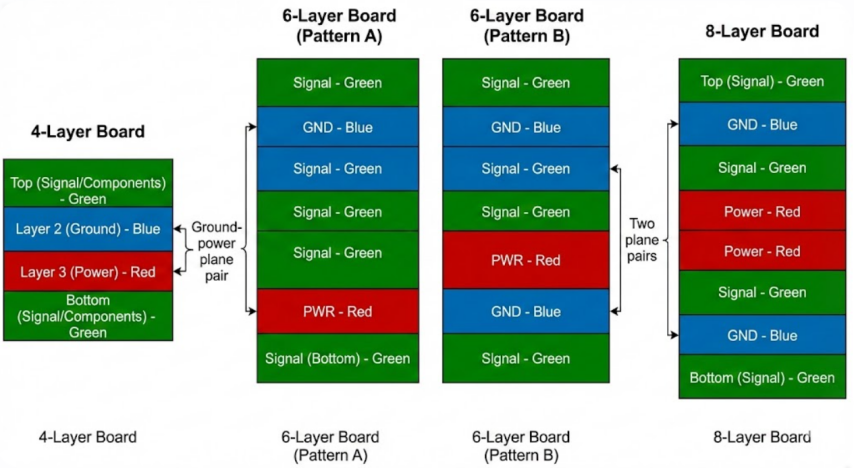

4、6、8 層板的常見疊層範例

1) 4 層板:常見疊層為 Top(訊號/元件)- Layer2(接地)- Layer3(電源)- Bottom(訊號/元件)。在嵌入式與 RF 模組專案中常見,兼顧走線密度、阻抗控制與成本。

2) 6 層板:兩種常用配置:

- Pattern A:訊號 接地 訊號 訊號 電源 訊號(底)

- Pattern B:訊號 接地 訊號 電源 接地 訊號

Pattern A 多一內層訊號,有助紓解走線;Pattern B 把電源平面夾在兩接地平面間,抗雜訊能力佳。需良好配電時選 A,雜訊免疫力優先時選 B。

3) 8 層板:常見疊層:Top(訊號) 接地 訊號 電源 訊號 接地 Bottom(訊號)。中間兩層電源,第 2 與第 7 層為接地,是高速設計的黃金法則,多重平面配對縮小迴路面積並降低輻射。

兼顧厚度與材料以達成性能

銅厚/銅重:厚銅可載更大電流並散熱,但會影響阻抗。銅越厚,要維持相同阻抗就得加寬或加間距。疊層時依需求選擇銅重。

介質厚度:走線阻抗直接取決於訊號層與參考平面的距離。例如 1.6 mm 板厚、Dk≈4.2 時,5 mil(0.127 mm)走線在距參考平面 0.2 mm 時約 50 Ω。介質變薄阻抗下降,變厚阻抗上升。

板厚與材料:一般硬板厚度 0.6–2.0 mm 以上,較厚板材散熱與支撐較佳;極薄板可撓但易翹曲或組裝破裂。

介電材料:FR-4 為常見標準,Dk≈4.3。RF 或超高速應用可選低損耗材料如 Rogers 或 PTFE 基材,Dk 與損耗因子更低,可減少訊號損失。板材也會影響疊層距離,JLCPCB 等提供的阻抗計算器可協助選厚。

遵守 PCB 層的標準與規範

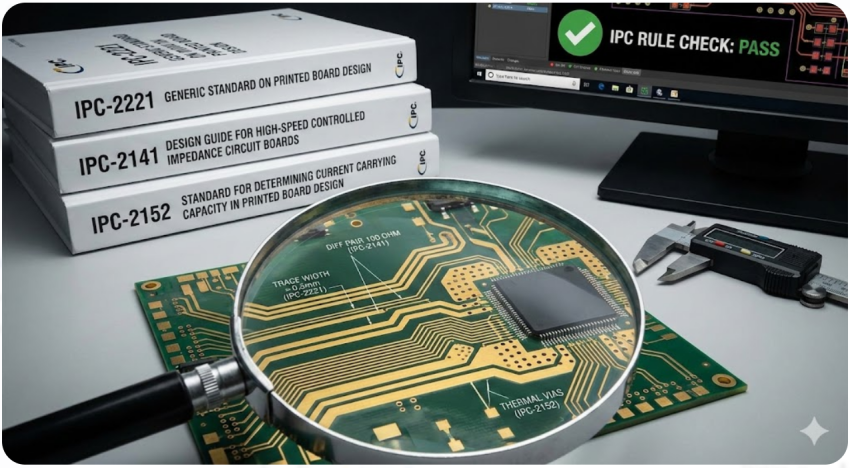

優質PCB 設計不能僅靠直覺,須遵循業界標準與最佳實踐。IPC(Institute for Printed Circuits)即為最常見的標準:

- IPC-2221/2222(通用與硬板設計):定義線寬、間距與疊層優化的通用規則,提供計算特定電流下最小線寬的公式,確保走線不過熱、不電弧,並有足夠介電間距。

- IPC-2141(高速設計):針對高速板的訊號完整性與阻抗控制提供建議,說明如何設計走線與疊層以減少反射與損耗,維持差動與單端阻抗。

- IPC-2152(熱管理):協助計算安全走線厚度與熱隔離,讓發熱元件安全散熱,指導銅平面與散熱過孔的設計。

遵循這些標準可提升可靠度、簡化製造並符合法規。多數 PCB CAD 軟體內建 IPC 規則檢查器,可在設計階段自動把關。

阻抗控制與層對稱需求

1) 控制阻抗:高速線通常要求單端 50 Ω、差分 100 Ω。阻抗由走線幾何與到參考平面的介質間距決定。先固定疊層,再調線寬/間距達標。IPC 與板廠疊層表可提供參考值,JLCPCB 的阻抗計算器會依板材厚度給出建議線寬。

2) 層對稱:高品質阻抗板通常以中心對稱,介質厚度與銅分布上下鏡像,避免兩側固化或膨脹速率不同導致翹曲。不對稱疊構「會在製程中翹曲,進而影響訊號完整性」。設計時可在規格書中明確要求對稱疊層。

3) 訊號對走線:差動對與其他等長網路應走在同一層,保持等長等間距以維持阻抗平衡。Sierra Circuits 建議長度誤差控制在數 mil 內,並保持對稱避免偏移。若非得換層,兩線應一起經同一過孔。

高速設計的層分配規則

- 專屬參考平面:每條高速線都要有乾淨的迴流路徑,通常是在同一層正下方放置完整接地平面。缺乏連續平面時,迴流繞遠路會產生雜訊與抖動。

- 避免平面分割:不要讓高速線跨越平面分割區;若必須跨越,加縫合過孔在該處連接兩側平面。

- 類比數位分離:混合訊號設計中,將類比與數位區域分配不同層或獨立銅區,避免數位切換雜訊干擾敏感類比走線。

- 差動對:維持固定間距與參考平面,確保疊層提供正確差分阻抗。

進階 PCB 層設計技巧

跨多層的走線策略

- 訊號分組:把相關匯流排訊號放在同一層,例如位址線一層、資料線另一層,整齊且利於時序分析。

- 減少過孔:每個過孔都帶寄生電容與電感。

- 縫合過孔:在敏感區周圍與連接器附近放置接地過孔「圍籬」,把平面連在一起,提供局部迴流。

透過層選擇抑制熱與 EMI

熱擴散:銅導熱佳,內層銅平面本身就是散熱片。多層板銅量多,可均熱。高功耗設計可專闢內層平面並加散熱過孔把熱導至平面。

EMI 遮蔽:完整平面本身就是輻射遮蔽。多重接地/電源配對可縮小訊號電流迴路面積,8 層板因平面配對多,EMI 性能優異。

常見 PCB 層問題與排除

即使事先規劃,問題仍可能發生。以下說明如何辨識與解決常見層相關問題:

由疊層不良導致的訊號完整性問題

訊號行為異常常可追溯到疊層缺陷,例如介質不均導致阻抗突變,進而在高速線上看到反射或位元錯誤。

診斷方法:

- 用示波器與 TDR 眼圖觀察反射,確認是否因層間距錯誤導致阻抗不匹配。

- 檢查迴流路徑,用接地連續性測試或模擬確認每個訊號層的相鄰平面確為接地。

- 檢視不同層的平行走線是否因共享去耦不良的平面而互相干擾。

把症狀與層配置對照,通常可鎖定問題層。

解決串擾、雜訊與翹曲

串擾與雜訊:兩相鄰訊號線能量互相耦合即產生串擾。解決方式:加大線距、中間加接地層、把其中一條改走到已有接地參考的層,並在電源-接地平面間靠近元件處加去耦電容。雜訊過大時可在干擾源間插入細接地平面或保護走線。

翹曲:成品板彎曲主因是疊構不對稱。重新安排銅箔與預浸材,使疊構上下鏡像,例如中線以上介質與銅厚須與以下相等,兩面使用相同數量的含銅芯板。業界經驗顯示,平衡疊構可讓大多數翹曲問題消失。

常見問題(FAQ)

Q:為何多層 PCB 需要這麼多層?

A:層數多可在小面積內走複雜電路,並提供獨立的電源與接地平面。每增加一層就多出佈線空間或完整銅面供電/接地。

Q:什麼是 PCB 疊構?

A:疊構就是板內所有銅層與絕緣層的垂直順序,簡單說就是 PCB「三明治」的排法。

Q:接地平面如何作用?

A:接地平面是完整銅箔,提供電流迴流路徑並兼做 EMI 遮蔽。放在訊號層正下方時,可縮短迴流路徑並維持走線特性阻抗。

Q:什麼原因造成串擾?如何降低?

A:兩平行走線間能量耦合即串擾。可加大線距或中間加接地層來降低。

Q:為何層對稱重要?不對稱會如何?

A:層對稱可保持板子平衡。若一側銅或介質厚於另一側,板子在製程與溫變中會翹曲或彎曲。

持續學習

PCB 板類型:規格與應用場景終極指南

印刷電路板(PCB)由絕緣層與導電層壓合而成,用於連接多個電子元件。可以把 PCB 想像成玻璃纖維與環氧樹脂疊成的複合板材,上面蝕刻出銅線路,作為訊號與電源的導電路徑。PCB 可以是單層、雙層(兩層導電層)或多層(三層以上導電層),在極小空間內容納大量電路。根據 IPC 的定義,PCB 是由導電與非導電材料經壓合後,形成電氣組件所需的電路。 官方 IPC 定義與層次結構 實務上,PCB 是由交替的介電層與銅箔層構成。銅層上佈有線路、平面、焊墊與通孔,用於連接元件。典型的 4 層 PCB 疊構可能如下: 銅層 – 預浸料或芯材 – 銅層 – 芯材 – 銅層 所有層次都經壓合固定。樹脂/玻璃基材提供機械強度與絕緣。IPC-2221 與 IPC-4101 標準規範了疊構幾何與材料特性。簡單來說,PCB 就是一塊多層三明治板,銅片(線路)負責導電,而非起司。 12 種核心 PCB 類型(2025 版) 工程師通常依結構與用途分類 PCB。以下為 2025 年最常見的 12 種基礎 PCB 類型: 單面 / 雙面 / 多層 單面板:僅有一層銅線路,成本最低,用於基本消費電子,如玩具、簡單電源電路。 雙面板:......

PCB 層數解析:透過智慧疊構、標準與設計實踐打造更優質的電路板

PCB 是由銅箔與絕緣層層疊而成的「三明治」,用來形成電路板。每一層都有特定功能:有些負責承載訊號(連接元件的走線),有些則作為完整的電源或接地平面。可以把 PCB 層想像成大樓的樓層,每層扮演不同角色,例如一層是辦公室(訊號),另一層是倉庫(接地/電源)。層數依設計複雜度而定,從單層到十幾層的高階電子產品都有。本文將說明如何有效安排這些層,降低 EMI 並提升訊號完整性,關鍵就在於佈線與配置的規劃。 單層與多層 PCB 的定義 最基礎的是單層 PCB,只有一面銅箔,製造成本低,適合 LED 驅動等低成本電路。 業界主流是雙層 PCB,上下兩面都有銅箔,走線選擇翻倍,兩層間透過稱為「過孔」的小孔互連訊號。 多層 PCB則使用三層以上銅箔,內部通常夾有電源與接地平面,並位於訊號層之間。手機、筆電、醫療設備等高密度產品都採用多層板,以滿足嚴格的雜訊管理需求。 從簡單到複雜的層配置演進 早期電子產品單雙層板即可應付,但隨著功能複雜與速度提升,設計者必須增加層數。每多一層就多出佈線空間,避免交叉。實際應用上,低階產品為成本考量維持 2–4 層;中階設計常見 6 層;高速高階系統則普遍 8 層以上。8 層板......

在 PCB 中整合間隔柱:機械可靠性與效能的關鍵考量

Standoff 間隔柱本質上是小型支柱,用於支撐電路板。它們遠不止是 PCB 組裝中的小零件。這些元件透過將 PCB 稍微抬高,讓空氣得以流通,從而提供更好的絕緣與機械支撐。Standoff 能固定電路板,防止其與其他零件接觸。選擇合適的 standoff 確實能帶來改變;它確保設備正常運作,而非故障或鬆脫。如此一來,它們能在零件下方創造空氣循環空間,這是合理的設計選擇。在密集排列中保持適當間距對於散熱與安全都極為重要。 確保穩固安裝與抗振能力 金屬 standoff 能在工業控制器與伺服器機殼之間穩定並支撐電路板,防止因移動而彎曲或斷裂。金屬 standoff 透過為電路板提供金屬支撐,防止大型電路板因過度移動而彎曲。緊固件(主要是螺絲)通常會搭配墊圈,為緊固接頭提供額外保護,防止過度鎖緊。為了妥善固定電路板,必須以能讓電路板承受多次負載與跌落等衝擊而不受損的方式放置緊固件與 standoff。Standoff 可視為避震器,為電路板提供安全的固定點。若電路板未使用 standoff,PCB 將因裂縫與短路而受損。 在密集布局中支援散熱與 EMI 屏蔽 透過將 PCB 抬離安裝表面,stand......

PCB 的生產與製造流程是什麼?

PCB 的創造者是一位名叫 Paul Eisler 的奧地利人。1936 年,他首次在收音機中使用印刷電路板。1948 年,美國正式認可這項發明並投入商業應用。自 1950 年代中期起,印刷電路板被廣泛採用。幾乎每台電子設備都包含 PCB。如果設備中有電子元件,它們都安裝在各種尺寸的 PCB 上。PCB 的主要功能是將各種電子元件連接起來,形成預定的電路,充當電信號傳輸的中繼站,常被稱為「電子產品之母」。 談到 PCB 的生產與製造,需要經過一系列步驟,以確保最終產品的品質與可靠性。以下是更多步驟與細節,幫助你更深入理解 PCB 的生產製造流程: 準備工作: 在開始生產前,需要準備 PCB 圖紙與相關資料。這些圖紙包含 PCB 尺寸、電路走線、元件佈局等資訊。主要設計與選擇的方面包括 PCB 基材 的類型、焊盤、導電走線等。 確定 板厚:根據圖紙要求,選擇合適的板厚(以毫米為單位)。 確定表面處理:決定板材的表面處理方式,如鍍金、鍍銀或熱風整平(HASL)。 指定元件類型與規格:確定所需的元件類型與規格,包括電阻、電容、二極體等。 準備工具與設備:收集製造過程中所需的工具與設備,如鑽孔機、成型機與......

PCB 基礎:6:新興趨勢與技術

談到學習 PCB 及相關電子的實用知識,不得不提新興趨勢與技術,才能掌握最新進展。PCB 無所不在! 今天,我們將深入探討從軟性 PCB、軟硬結合板到高密度互連(HDI)等技術的變革潛力,並討論物聯網(IoT)與穿戴式裝置對 PCB 設計的影響。 與我們一起踏上創新之旅,突破 PCB 技術的疆界! PCB 技術的突破: 讓我們探索幾項顛覆 PCB 設計的重大進展: A) 軟性 PCB: 軟性 PCB(flex PCBs)是卓越的進步,相較於傳統硬板更具彈性與耐用性。其採用聚醯亞胺或聚酯等柔性材料,可彎曲並貼合複雜形狀,特別適用於空間受限或需動態運動的場景,如醫療設備、汽車電子與消費性電子。 B) 軟硬結合板: 軟硬結合板整合硬板區與軟板區,兼具兩者優勢,可設計出複雜的三維電路。其高可靠度、小型化與優異訊號完整性,廣泛應用於航太、工業電子與穿戴裝置。 C) 高密度互連(HDI): HDI 是 PCB 技術的關鍵進展,能在更小尺寸內實現更高功能。透過微盲埋孔與先進製程,達到更高電路密度並縮短訊號傳遞延遲,支援多層板與更細線寬,實現小型化與高效能,常見於智慧型手機、平板等高效能電子產品。 IoT 與穿戴......

電路板設計的演進

歡迎來到 JLCPCB 的部落格,在這裡我們將深入探討 PCB 設計、製造與組裝的精彩世界。電路板經歷了非凡的演進,從簡單的單層設計轉變為複雜且多功能的 multi-layer 板。今天,我們將深入回顧電路板設計的演進歷程,追溯其從簡單單層板到複雜多層板的轉變。與我們一起探索推動電路板設計演進的歷史、優勢與進步。 從卑微的起點: 自誕生以來,電路板已經走過了漫長的道路。早期,單層板是常態。這些板子由單層導電材料(通常是銅)層壓在絕緣基板上。元件焊接在板子的一側,而另一側的走線提供必要的互連。雖然對基本電子設備有效,但單層板有其局限性。 單層板適用於元件較少、要求不高的簡單電子設備。然而,隨著技術的進步和對更複雜電子系統需求的增長,對更高連接性和功能性的需求導致了多層板的發展。 多層板的出現: 多層板徹底改變了 PCB 設計領域。它們由多層導電材料組成,這些導電層由絕緣層隔開,並透過 vias 互連。這些 vias 允許訊號在層間傳遞,實現更高的元件密度和更複雜的設計。 優勢與進步: 從單層板轉向多層板帶來了許多優勢。首先,多層板提供了更多的佈線選項,實現更高效的訊號路徑並減少電磁干擾。這提高了電子......