디자인 규칙 검사가 고가의 PCB 생산 실수를 방지하는 방법

2 분

- 설계 규칙 검사가 모든 PCB 프로젝트에서 중요한 이유

- 모든 설계자가 반드시 마스터해야 할 주요 DRC 규칙

- 워크플로우에서 효과적인 설계 규칙 검사 실행

- 강력한 DRC가 전문 제조에 미치는 이점

- JLCPCB의 고급 DRC 및 DFM 전문성

- 자주 묻는 질문 (FAQ)

거버 파일을 PCB 제조업체에 보냈더니, 클리어런스나 애뉼러 링 문제를 수정해야 생산을 시작할 수 있다는 이메일이 돌아온 경험이 있으신가요? 그런 상황을 겪어보셨다면 얼마나 답답한지 아실 겁니다. 며칠이 낭비되고, 리비전 번호는 올라가며, 출하 날짜는 밀려납니다. 이 모든 것을 미리 잡아내는 것이 좋은 설계의 진정한 핵심입니다. 바로 PCB 레이아웃 도구의 탄탄한 설계 규칙 검사(DRC)를 통해 파일이 책상을 떠나기 전에 문제를 발견할 수 있습니다.

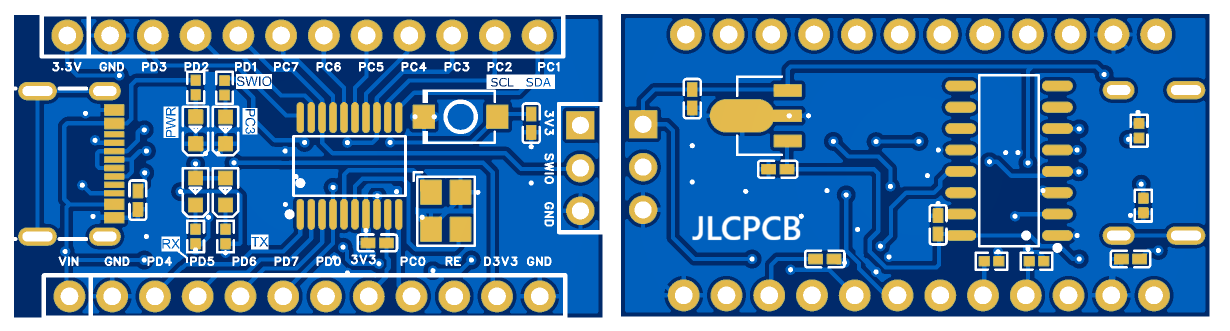

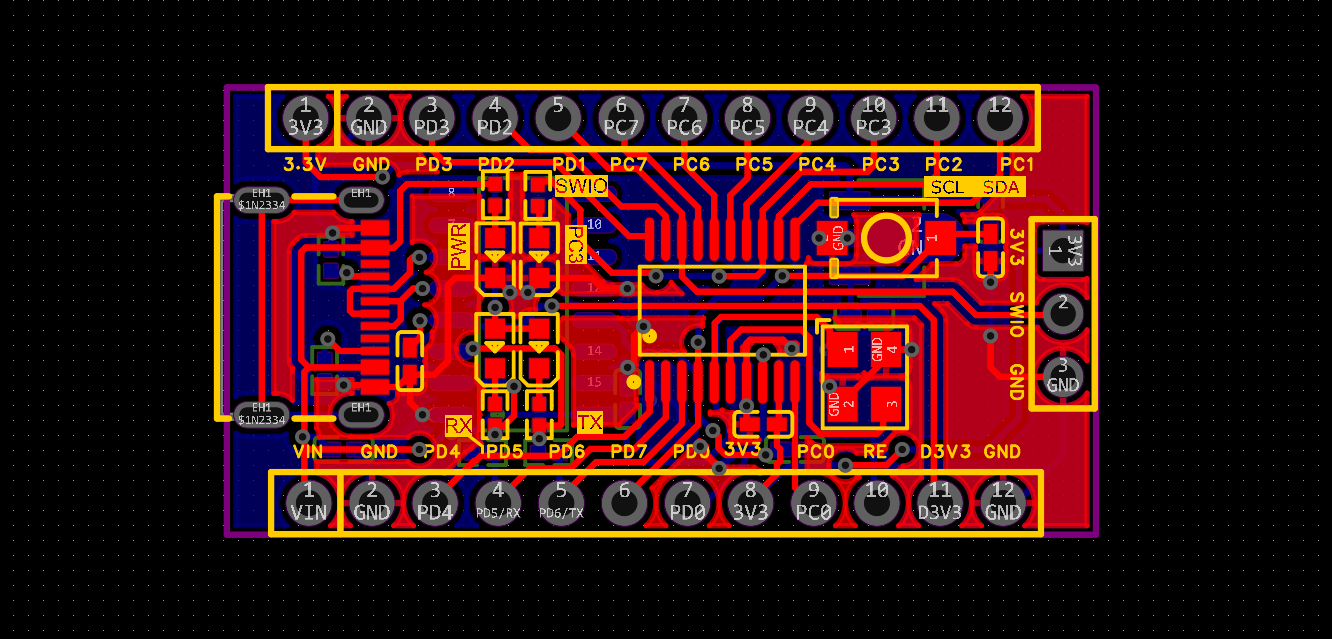

이것은 좁은 보드에서 더욱 중요합니다. 35개 넷, 41개 관통 비아, 29개 부품이 담긴 작은 34.9mm×17.9mm CH32V003 개발 보드를 생각해 보세요. 이런 작은 보드에서는 모든 것을 쥐어짜 넣어야 하므로 클리어런스 1밀리미터 하나도 허투루 쓸 수 없습니다. USB 입력 섹션이나 크리스탈 넷 PA1/PA2와 MCU 코어 사이에 위반 사항이 하나만 더 추가되면, 빠르게 완성될 뻔했던 프로토타입이 비용이 많이 드는 재설계로 이어질 수 있습니다.

오늘은 DRC가 실제로 어떻게 작동하는지, 어떤 규칙을 반드시 마스터해야 하는지, 설계 흐름에서 언제 검사를 수행해야 하는지, 그리고 깔끔한 DRC 파일이 어떻게 더 저렴하고 빠른 제조로 이어지는지 알아보겠습니다. 이 가이드는 첫 번째 2층 보드를 배치하는 분이든 양산 설계를 다듬고 있는 분이든 작업 프로세스를 한 단계 끌어올려 줄 것입니다.

설계 규칙 검사가 모든 PCB 프로젝트에서 중요한 이유

현대 설계 흐름에서 DRC의 역할 이해

설계 규칙 검사(DRC)는 창의적인 레이아웃 작업과 PCB 제조의 물리적 현실 사이에 자리 잡은 자동화된 안전 장치입니다. 모든 제조업체는 일련의 제조 제약 조건 내에서 운영됩니다: 최소 트레이스 폭, 구리 요소 간 최소 간격, 가장 작은 신뢰할 수 있는 드릴 직경, 그리고 필요한 애뉼러 링 크기. DRC는 이러한 제약 조건을 EDA 도구 내에서 시행 가능한 규칙으로 변환합니다.

DRC를 번역가로 생각해 보세요. 제조업체의 능력 사양을 레이아웃 편집기가 보드의 모든 트레이스, 패드, 비아, 클리어런스에 대해 검사할 수 있는 디지털 규칙 세트로 변환합니다. CH32V003 보드의 고밀도 MCU 코어 영역에서 트레이스를 비아에 너무 가깝게 라우팅하면, DRC가 생산으로 넘어가기 전에 즉시 플래그를 표시합니다.

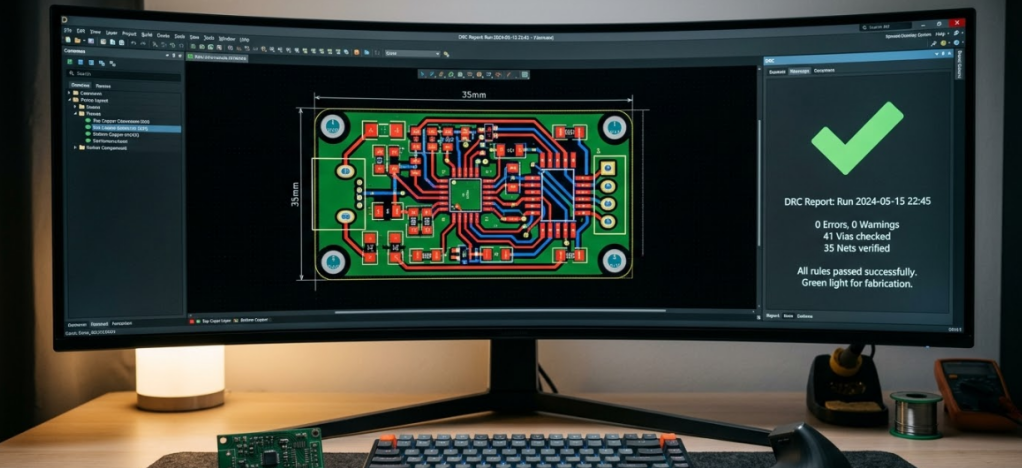

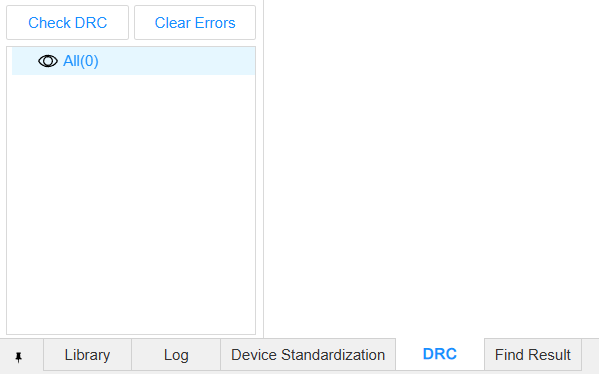

많은 설계자들이 놓치는 중요한 포인트가 있습니다: DRC는 한 번만 하는 최종 검사가 아닙니다. 플로어플래닝 후, 각 기능 블록 라우팅 중, 그리고 거버 출력 전에 다시 한 번 실행해야 합니다. 각 단계는 수정 비용이 가장 저렴한 시점에 서로 다른 범주의 오류를 포착합니다.

생산에서 DRC를 건너뛰는 높은 비용

설계 검토를 통과하지 못한 위반 사항은 제조 또는 어셈블리 단계에서 물리적 결함이 됩니다. D+/- USB 차동 쌍과 인접한 그라운드 쏟아붓기 사이의 클리어런스 위반은 화면에서는 별거 아닌 것처럼 보일 수 있습니다. 하지만 제조업체에서 그 위반은 에칭 후 구리 단락을 초래하여 완성된 패널을 불량품으로 만들 수 있습니다.

CH32V003 참조 설계와 같은 콤팩트한 보드에서 이런 문제는 빠르게 나타납니다. 약 630 평방밀리미터의 보드 면적에 29개 부품이 빽빽이 들어차 있어 솔더 마스크 슬리버와 구리 클리어런스의 오차 여유가 매우 좁습니다. 더 큰 보드에서 겨우 통과하는 마스크 개구부가 여기서는 확실한 결함이 됩니다.

DRC를 건너뛰면 첫 번째 제품 승인도 지연됩니다. 많은 설계자들은 라우팅이 명백한 오류 없이 완료되었기 때문에 레이아웃이 깨끗하다고 가정합니다. 하지만 제조업체들은 거버 파일에 자체 DFM 검사를 실행하며, 문제를 발견하면 주문이 보류됩니다. 그 보류는 48시간에 출하될 예정이었던 작업에 3~5일을 추가할 수 있습니다.

모든 설계자가 반드시 마스터해야 할 주요 DRC 규칙

클리어런스, 간격, 애뉼러 링 요구사항

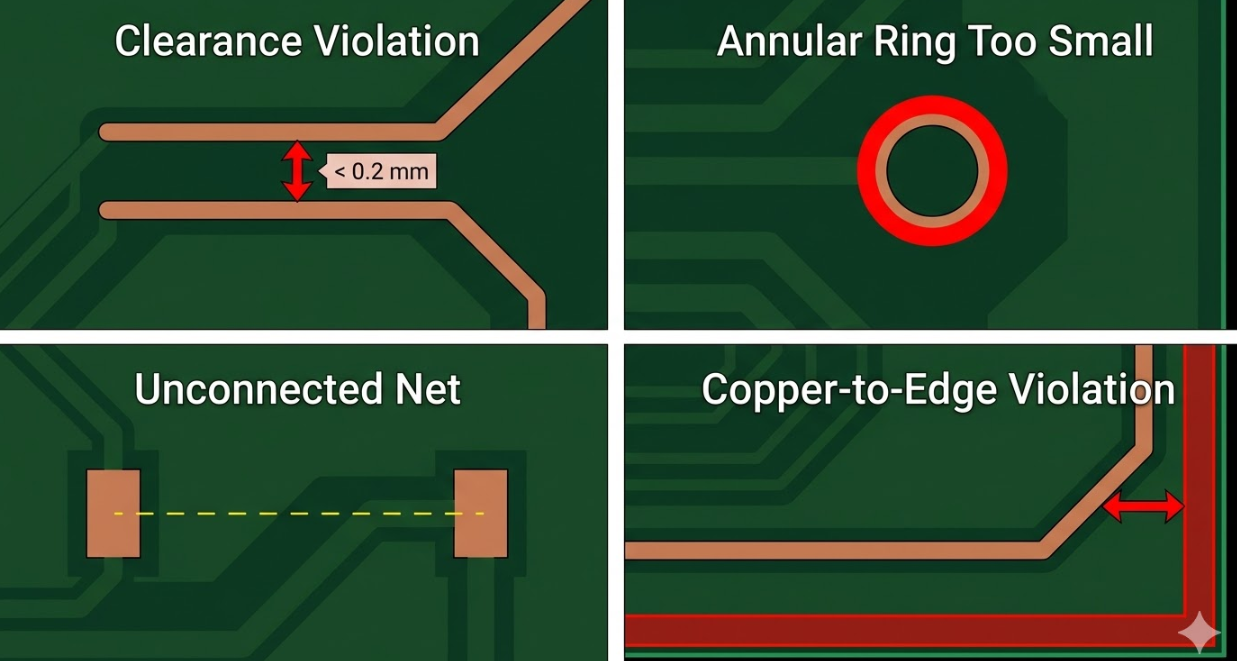

클리어런스 규칙은 DRC를 설정할 때 따라야 하는 기본 규칙과 유사합니다. 트레이스 간, 트레이스와 패드 간, 패드와 비아 간, 심지어 구리와 보드 엣지 간 등 모든 구리 부분 사이의 최소 간격을 설정해야 합니다. 주류 제조업체가 사용하는 일반적인 2층 보드의 경우 0.2mm(약 8mil)의 클리어런스가 일반적으로 충분합니다. 한계를 밀어붙일 때는 많은 제조업체가 0.1mm(4mil)까지 가능하지만 에칭 및 이미징 공정을 면밀히 모니터링해야 합니다.

애뉼러 링은 보드를 만들 때 드릴된 홀에 남아 있는 구리 링입니다. 드릴이 약간 빗나가면 애뉼러 링이 너무 작아져 패드 연결이 끊길 수 있습니다. IPC-6012 Class 2는 내층(및 외층) 모두 최소 애뉼러 링 직경 0.05mm(2mil)를 규정하지만, 외층에서 0.15mm(6mil)를 유지하는 것이 신뢰할 수 있는 생산을 보장하는 더 안전한 관행입니다.

구리와 보드 엣지 클리어런스도 잊지 마세요. IPC-2221에 따르면 라우팅으로 인한 구리 박리를 방지하기 위해 구리는 보드 엣지에서 0.25mm 이상 떨어져야 합니다. CH32V003 보드에서는 특히 USB 커넥터 주변에서 트레이스가 보드 외곽선 가까이 달리는 부분을 이중으로 확인해야 합니다.

| DRC 규칙 | 안전한 기본값 (2층) | 고급 역량 | IPC 참조 |

| 트레이스 간 클리어런스 | 0.2mm (8mil) | 0.1mm (4mil) | IPC-2221 |

| 트레이스-패드 클리어런스 | 0.2mm (8mil) | 0.1mm (4mil) | IPC-2221 |

| 애뉼러 링 (외층) | 0.15mm (6mil) | 0.075mm (3mil) | IPC-6012 |

| 구리-보드 엣지 클리어런스 | 0.25mm (10mil) | 0.2mm (8mil) | IPC-2221 |

| 솔더 마스크 슬리버 | 0.1mm (4mil) | 0.05mm (2mil) | IPC-7525 |

트레이스 폭, 비아 규칙, 구리 밸런스 가이드라인

트레이스 폭은 두 가지 주요 요인, 즉 전류 전달 능력과 제조 용이성에 의해 결정됩니다. CH32V003 보드에서 몇 밀리암페어만 흐르는 신호 트레이스에는 0.15mm(6mil) 폭으로 충분합니다. 그러나 MCU와 USB-to-TTL 변환기에 전력을 공급하는 3V3 전원 레일은 더 넓은 트레이스가 필요합니다. 1온스 구리 외층 트레이스에서 적당한 온도 상승으로 최대 500mA의 전류는 0.3~0.5mm 폭으로 잘 처리할 수 있습니다.

비아 규칙은 드릴 직경과 완성 홀 대 패드 비율을 제한합니다. 0.3mm 드릴과 0.6mm 패드를 가진 표준 관통 홀 비아는 충분한 애뉼러 링과 신뢰할 수 있는 도금을 제공합니다. CH32V003 보드는 41개의 관통 비아를 사용하므로 일관된 비아 크기는 제조업체가 드릴 프로그램을 최적화하고 패널 전체의 도금 균일성을 개선하는 데 도움이 됩니다.

구리 밸런싱은 DRC에서 자주 간과되지만 실제 제조에 영향을 미치는 규칙입니다. 2층 보드의 한쪽에 다른 쪽보다 구리가 훨씬 많으면 라미네이션과 리플로우 시 보드가 휘는 경향이 있습니다. CH32V003 보드에서는 하단 레이어에 그라운드 쏟아붓기가 있다면 상단 레이어에도 적절한 구리 커버리지를 확보하세요. 이는 휨을 줄이고 에칭 균일성을 향상시킵니다.

| 비아 파라미터 | 표준값 | 비고 |

| 드릴 직경 | 0.3mm (12mil) | 신호 비아에 가장 일반적 |

| 패드 직경 | 0.6mm (24mil) | 0.15mm 애뉼러 링 제공 |

| 종횡비 (보드 두께 : 드릴) | 최대 8:1 | 1.6mm 보드의 신뢰할 수 있는 도금을 위해 |

| 비아 간 간격 | 0.5mm (20mil) | 인접한 비아 사이의 드릴 이탈 방지 |

| 비아-트레이스 클리어런스 | 0.2mm (8mil) | 넷 클래스 클리어런스 최소값 맞춤 |

워크플로우에서 효과적인 설계 규칙 검사 실행

핵심 단계에서 커스텀 규칙 설정 및 DRC 실행

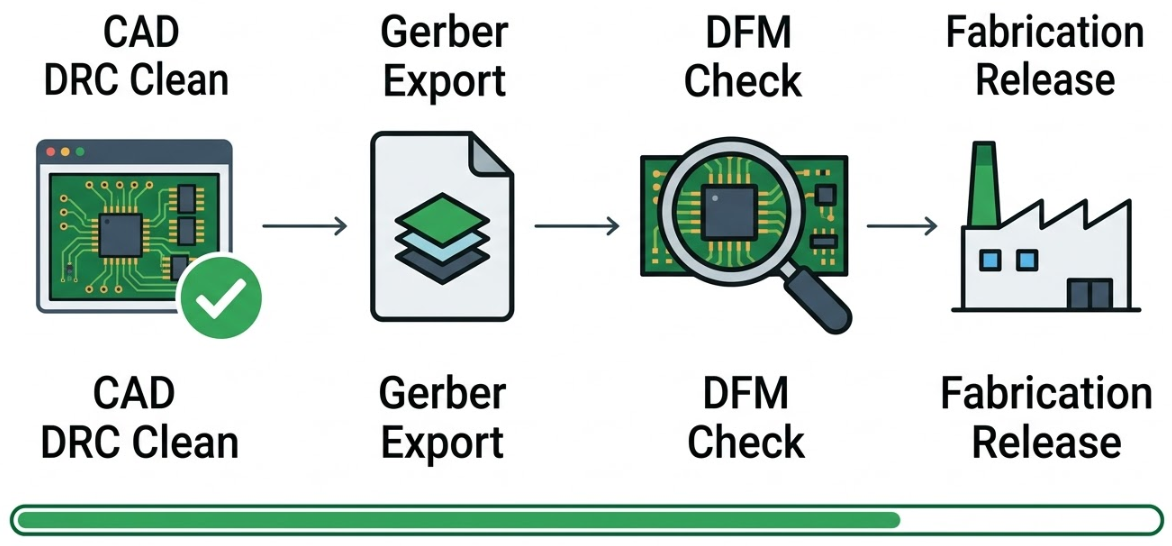

올바른 시점에 DRC를 실행하는 것은 올바른 규칙을 정의하는 것만큼 중요합니다. CH32V003 참조 설계와 같은 보드에서 잘 작동하는 3단계 워크플로우를 소개합니다:

- 플로어플랜 후 DRC: 부품 배치, 보드 외형 정의, 레이어 스택 및 설계 규칙 설정 직후에 실행합니다. 이 단계에서는 코트야드 겹침, 부품-엣지 클리어런스, 넷 클래스 규칙 정의를 검사합니다. CH32V003 보드에서는 USB 커넥터 풋프린트가 보드 엣지를 넘거나 고밀도 MCU 코어 영역에서 부품 코트야드가 겹치는 문제를 포착합니다.

- 블록 수준 DRC: 각 기능 블록의 라우팅을 완료한 후 실행합니다. 전원 섹션(3V3 레귤레이터, 입력 디커플링)을 먼저 라우팅하고 DRC를 실행한 다음, 클록 네트워크(크리스탈 넷 PA1/PA2)를 라우팅하고 다시 DRC를 실행한 후, USB D+/- 쌍, SWIO 디버그 인터페이스, GPIO/프로그래밍 헤더를 처리합니다. 각 검사는 다음 블록의 라우팅 복잡성을 추가하기 전에 현재 블록이 깨끗한지 확인합니다.

- 최종 전체 보드 DRC: 거버 파일, BOM, 부품 배치 목록(CPL)을 생성하기 전에 모든 규칙이 활성화된 완전한 DRC를 실행합니다. 이것이 블록 간 상호작용을 포착할 마지막 기회입니다. 예를 들어, 2단계에서 라우팅된 전원 트레이스가 2단계의 클록 라우팅에서 추가된 신호 트레이스와 클리어런스 위반을 일으키는 경우입니다.

각 단계에 커스텀 규칙을 설정하면 오탐을 방지할 수 있습니다. 1단계에서는 아직 트레이스가 없으므로 라우팅 관련 검사(트레이스 폭, 비아 규칙)를 비활성화할 수 있습니다. 3단계가 되면 예외 없이 모든 규칙이 활성화되어야 합니다.

보고서 해석 및 중요 수정 사항 우선순위 결정

중간 복잡도의 보드에 대한 DRC 보고서는 수십 개의 위반 사항을 반환할 수 있습니다. 모든 위반이 동일한 비중을 갖지는 않습니다. 올바르게 우선순위를 정하면 시간을 절약하고 작업을 막는 실제 문제를 먼저 수정할 수 있습니다.

이 순서로 위반 사항을 우선시하세요:

1. 하드 제조 차단 요소: 구리 단락, 제조업체의 최소 역량 이하의 클리어런스 위반, 애뉼러 링 위반, 미연결 넷이 포함됩니다. 35개 넷과 0개의 미라우팅 넷을 가진 CH32V003 보드에서 DRC 보고서에 미연결 넷이 나타난다면 편집 중에 무언가 잘못되었다는 의미로 즉각적인 주의가 필요합니다.

2. 신뢰성 위험: 노출된 패드와 겹치는 실크스크린, 촘촘한 패드 사이의 솔더 마스크 슬리버, 그라운드 플레인 연결의 약한 써멀 릴리프. 이것들이 반드시 제조를 중단시키지는 않지만 어셈블리 결함을 유발하고 장기 신뢰성을 낮춥니다.

3. 외관 및 권고 경고: 선호 값보다 약간 넓은 트레이스 간 간격, 텍스트 배치 권고사항, 구리 밸런스 권고사항. 시간이 허락하면 수정하되 이것들 때문에 양산 출시를 미루지 마세요.

의도적으로 수락하는 위반 사항에 대해 예외 로그를 유지하세요. 라우팅 토폴로지가 요구하기 때문에 NRST 리셋 회로의 패드에 기본 최소값보다 비아를 더 가깝게 배치했다면, 실제 측정된 클리어런스와 엔지니어링 근거를 함께 예외로 문서화하세요. 이 로그는 다른 엔지니어가 설계를 검토하거나 몇 달 후 보드를 재검토할 때 매우 유용합니다.

강력한 DRC가 전문 제조에 미치는 이점

수정 횟수 및 생산 지연 감소

거버 파일이 DRC 위반 사항 없이 제조업체에 도착하면 CAM 엔지니어링 팀이 더 빠르게 승인할 수 있습니다. 묻고 싶은 것도 없고, "엔지니어링 보류" 이메일도 없으며, 좁은 클리어런스가 의도적인지 실수인지에 대한 주고받기도 없습니다. 1~2일 생산 시간을 약속하는 빠른 프로토타입 서비스의 경우, 깔끔한 파일 세트가 그 일정을 맞추느냐 놓치느냐의 차이를 만듭니다. DRC 클린 설계는 수정 횟수도 줄입니다. 모든 보드 재설계는 제조 비용뿐만 아니라 엔지니어링 시간, 부품 조달 지연, 일정 위험 측면에서도 비용이 발생합니다.

레이아웃이 촘촘하지만 특별히 복잡하지 않은 CH32V003 설계와 같은 콤팩트한 보드에서는 놓친 DRC 위반으로 인한 피할 수 있는 재설계를 수용할 이유가 없습니다. JLCPCB와 같은 현대 PCB 제조업체는 매일 수천 개의 설계를 처리합니다. DFM 스크리닝을 플래그 없이 통과하는 보드는 바로 생산 큐로 이동합니다. 문제가 있는 보드는 수동 검토를 위해 플래그가 표시되고 그 검토에는 시간이 걸립니다. 여러분 쪽의 강력한 DRC 규율은 제조업체 쪽의 더 빠른 처리로 직결됩니다.

수율 향상 및 전체 비용 절감

깔끔한 드릴 파일, 잘 정의된 구리 형상, 올바르게 크기가 지정된 마스크 개구부는 제조 수율을 직접적으로 향상시킵니다. 모든 비아에 적절한 애뉼러 링이 있으면 드릴-패드 레지스트레이션 허용 오차에 여유가 생깁니다. 모든 트레이스가 최소 폭을 충족하면 에칭 공정이 패널 전체에서 일관된 결과를 냅니다. 어셈블리 측면에서 올바른 솔더 마스크 개구부와 정확한 패드 형상은 솔더 브리징, 툼스토닝, 솔더 불량 결함을 줄입니다.

미세 피치 IC 패드와 관통 홀 커넥터가 혼재하는 CH32V003 보드에서 이러한 형상 세부 사항은 첫 번째 어셈블리 수율에 중요합니다. 비용 영향은 대량 생산 시 복합됩니다. 1,000개 보드 생산에서 2% 수율 향상만으로도 소재, 어셈블리 시간, 재작업 인건비에서 20개 보드 분량이 절약됩니다. 여러 생산 운영에 걸쳐 DRC 클린 설계로 인한 누적 절감액은 상당합니다. 재작업이 줄면 보드당 실질 비용이 낮아지고 모든 주문의 일정 위험이 감소합니다.

JLCPCB의 고급 DRC 및 DFM 전문성

빠르고 신뢰할 수 있는 피드백을 위한 내장 DRC 검증

DRC는 설계를 지정한 규칙과 비교하는 CAD의 내장 기능입니다. 하지만 고려하지 않은 규칙은 어떻게 될까요? 바로 그곳에서 외부 DFM 검증의 두 번째 레이어가 제공됩니다. JLCDFM은 JLCPCB가 무료로 제공하는 다운로드 가능한 도구입니다. 거버 파일을 분석하여 실제 생산 라인에서 제조 가능한 내용과 비교합니다.

JLCDFM은 일반 DRC를 초과하는 문제를 식별합니다: 예각 트레이스 접합부의 산 트랩, 신뢰할 수 있게 에칭할 수 없는 너무 좁은 구리 슬리버, 보드 엣지에 너무 가까운 드릴 히트, 처리를 지탱하기에 너무 얇은 솔더 마스크 댐. 이런 것들은 실제 제조 공정에 특화되어 있어 일반 CAD DRC에는 없는 유형의 문제입니다.

CAD DRC 이후 JLCDFM을 실행하는 것은 실제 생산 데이터를 기반으로 한 두 번째 의견을 받는 것입니다. CH32V003 보드에서는 USB 커넥터 패드 사이의 좁은 간격과 MCU 미세 풋프린트를 검사할 때 특히 유용합니다. 맞춤법 검사기와 교정 편집자의 차이처럼 생각해 보세요. 각각 실수를 수정하지만 다른 종류의 실수를 수정합니다.

설계에서 고품질 제조로의 원활한 전환

PCB 작업의 최선의 접근 방식은 단순하게 만드는 것입니다: 레이아웃을 잠그고, CAD DRC를 깨끗해질 때까지 실행하고, 거버 및 드릴 파일을 생성하고, JLCDFM을 실행하고, 나오는 문제를 수정한 후 제조 의뢰합니다. 이 2단계 검증은 보드가 공장 큐에 도달하기 전에 거의 모든 제조 가능성 문제를 포착합니다. CH32V003 보드에서는 이를 반복하기가 매우 간단합니다. 회로도를 변경하거나 레이아웃을 수정하거나 부품을 바꿀 때마다 단계를 반복하면 됩니다.

JLCPCB는 표준 보드 $2부터 시작하는 빠른 프로토타입 처리와 전체 검증 및 제작 프로세스를 간소화하는 자체 DFM 도구를 갖추고 있어 선택하기 좋은 곳입니다. SMT 어셈블리도 제공하며 최대 1~2일 내에 납품 가능합니다. 따라서 깔끔한 설계 파일과 실제 테스트된 보드 사이의 시간 간격이 그 어느 때보다 짧아졌습니다.

자주 묻는 질문 (FAQ)

Q1: 제조를 완전히 차단하는 DRC 오류는 무엇인가요?

구리 단락, 제조업체 최소 역량 이하의 넷 클리어런스 위반, 드릴링 후 패드 연결을 잃을 위험이 있는 애뉼러 링 위반, 미연결 넷이 모두 하드 차단 요소입니다. 이 중 어느 것이든 제조업체가 파일을 거부하거나 비기능적인 보드를 초래할 수 있습니다.

Q2: 소형 2층 MCU 보드에서 초기 클리어런스/폭/비아 규칙을 어떻게 설정해야 하나요?

신호 트레이스에 최소 클리어런스 0.2mm(8mil), 최소 트레이스 폭 0.15mm(6mil), 전원 넷에 0.3mm(12mil), 0.6mm 패드의 0.3mm 드릴 비아로 시작하세요. 이 값들은 대부분의 주류 PCB 제조업체에서 신뢰할 수 있게 작동합니다.

Q3: CAD DRC만으로 충분한가요, 아니면 외부 DFM 검사도 실행해야 하나요?

CAD DRC는 설계를 정의한 규칙에 대해 검사합니다. JLCDFM과 같은 외부 DFM 도구는 거버 출력을 실제 제조 공정 제약, 즉 산 트랩, 구리 슬리버, 마스크 댐 폭, 드릴-엣지 거리에 대해 검사합니다.

Q4: 반복적인 라우팅 중 DRC를 얼마나 자주 실행해야 하나요?

각 주요 라우팅 블록이 완료된 후 DRC를 실행하세요. CH32V003 보드에서는 전원 섹션 라우팅 후, 크리스탈 및 클록 넷 후, USB 인터페이스 후, GPIO 및 프로그래밍 헤더 후에 실행합니다. 거버 출력 전 최종 전체 보드 DRC로 블록 간 상호작용을 포착합니다.

지속적인 성장

CTE 불일치 스트레스 감소: 더 신뢰할 수 있는 PCB를 위한 실용적인 방법

핵심 요약 CTE 불일치(FR4의 높은 Z축 CTE 대 구리)는 무연 리플로우 및 열 사이클링 하에서 더욱 악화되는 PCB 휨, 비아 균열, 층간 박리, 솔더 피로를 유발하는 열응력을 만들어냅니다. 대칭 스택업과 균형 잡힌 구리 배분, 고Tg/저CTE 재료, 엄격한 공정 제어(적층, 냉각, 수분, 일관된 비아 도금)로 완화하세요. 표준 FR4의 Z축 열팽창계수가 최대 70 ppm/°C에 달하는 반면 구리는 17 ppm/°C에 불과하다는 것을 알고 계셨나요? 보드가 가열될 때 이 두 재료의 팽창은 4배나 차이가 납니다. CTE 불일치라고 불리는 이 차이가 인쇄 회로 기판의 휨, 솔더 조인트 균열, 층간 박리의 가장 빈번한 근본 원인 중 하나입니다. 리플로우 후 구부러진 PCB나 도금 관통홀의 불가사의한 배럴 균열을 경험하셨다면 CTE 불일치가 원인이었을 가능성이 높습니다. 더 얇은 보드, 더 작은 부품, 더 높은 무연 리플로우 온도로 인해 이 열팽창 차이를 관리하는 것은 그 어느 때보다 중요한 ......

UL94 V0이 안전한 PCB 제조에 중요한 이유

핵심 요약 UL94 V0는 PCB 재료의 최고 난연 등급으로, 불꽃 방울 없이 10초 이내 자기 소화를 요구합니다. 화재 위험을 크게 줄이며 소비자, 산업, 자동차, 의료 분야에서 안전하고 신뢰할 수 있는 PCB의 사실상 표준이 되었습니다. JLCPCB는 기본적으로 UL94 V0 규정 준수 FR4 및 고Tg 재료를 제공하여 성능이나 예산을 희생하지 않고 규제 준수(UL, CE, CCC)와 장기적인 신뢰성을 보장합니다. 소폭의 비용 절감을 위해 V0 등급을 희생하지 마세요. 거의 모든 회로 기판 앞면에 있는 작은 인쇄 문자를 본 적이 있으신가요? 바로 노트북, 휴대폰 충전기, LED 드라이버 내부의 보드 말입니다. 그 작은 마크가 전자제품 생산에서 가장 중요한 안전 등급 중 하나입니다. UL94 V0는 Underwriters Laboratories가 발표한 난연성 표준으로, PCB 기판 재료가 화염 원천이 제거된 후 10초 이내에 자기 소화됨을 알려줍니다. 왜 신경 써야 할까요? UL, CE, ......

안전한 PCB를 위한 올바른 UL94 등급 선택 방법

핵심 요약 이 글은 PCB 화재 안전 및 규정 준수를 위한 올바른 UL94 등급 선택 방법을 설명합니다: V-0는 대부분의 전자제품의 일반적인 기준이며, V-1/HB는 주로 규제가 덜한 용도에 사용됩니다. 또한 등급 성능이 재료 선택, 두께, 공정 제어에 달려 있다고 강조하므로, UL 인증 라미네이트와 추적 가능한 UL 인증 제조업체를 이용하세요. 단 하나의 PCB 화재가 유독 가스를 발생시키고 전체 제품을 소멸시키며 회사를 심각한 법적 위험에 빠뜨릴 수 있다는 것을 들어본 적 있으신가요? 바로 이것이 UL94 등급이 존재하는 이유입니다. 플라스틱 및 폴리머 재료의 가장 잘 알려진 난연성 분류 시스템으로, 인쇄 회로 기판을 최대한 안전하게 만드는 핵심 요소입니다. 간단한 LED 드라이버를 설계하든 복잡한 자동차 제어 모듈을 설계하든, PCB 기판의 난연성은 무시할 수 없습니다. 북미, 유럽, 아시아의 규제 기관들은 제품이 판매될 수 있으려면 특정 UL94 화염 등급을 요구합니다. 이 규정을 무......

유리전이온도가 PCB 신뢰성의 핵심인 이유

갓 리플로우를 마친 PCB 묶음을 오븐에서 꺼냈는데 층간 박리 물집이나 배럴 비아 균열이 발견된 경험이 있으신가요? 그런 경우라면 원인이 리플로우 프로파일이나 솔더 페이스트가 아닐 수 있습니다. 보드를 구성하는 기판 재료에 문제가 있을 수 있습니다. PCB 라미네이트의 물성 중 제조 공정을 통과하여 현장에서 사용되기까지 결정적인 차이를 만드는 가장 중요하면서도 자주 간과되는 특성이 바로 라미네이트의 유리전이온도입니다. PCB 생산에 사용되는 모든 수지 시스템은 특정 온도 이하에서 단단하고 유리 같은 물질처럼 작동합니다. 그 한계를 넘으면 수지가 부드러워지고 팽창률이 급격히 상승하며 기계적 강도가 저하되기 시작합니다. 그 온도가 바로 유리전이온도로, 보통 Tg로 표기합니다. 업계가 무연 솔더링으로 전환하고 최고 리플로우 온도가 250~260°C에 달하는 지금, Tg에 대한 지식은 더 이상 선택 사항이 아닙니다. 양질의 보드를 원하는 모든 엔지니어에게 필수 지식입니다. 이 글에서는 유리전이온도가 ......

전문 PCB 제조에서 네일 베드 테스트의 이점

제조업체들이 어떻게 매일 수천 개의 PCB를 테스트하면서도 생산 라인을 느리게 만들지 않는지 궁금한 적이 있으신가요? 그 답은 네일 베드 테스트 장비라는 얼핏 보기엔 단순해 보이는 기기에 있는 경우가 많습니다. 이 플랫폼에는 수백 개의 소형 스프링 핀이 장착되어 있으며, 각각의 핀이 회로 기판의 특정 테스트 포인트에 매우 정밀하게 닿도록 정렬되어 있습니다. 보드가 공장 라인을 벗어나기도 전에 몇 초 만에 전체 PCB의 전기적 무결성, 단락, 개방 회로, 부품 결함을 검사할 수 있습니다. 어느 정도 수량으로 PCB를 제조하고 있다면 테스트는 선택이 아닙니다. 신뢰할 수 있는 제품 납품과 품질 보증 반품의 차이입니다. 네일 베드 테스트는 수십 년 전부터 전문 PCB 제조의 핵심 요소였으며, 플라잉 프로브와 같은 최신 테스트 방법이 보편화되었지만 대량 생산에서는 여전히 금본위를 유지하고 있습니다. 속도, 반복성, 결함 커버리지 측면에서 처리량이 중요한 상황에서는 대체하기 거의 불가능합니다. 오늘은 ......

고속 PCB 우수성을 위한 마이크로스트립 라인 설계 기법

PCB의 외부 레이어에 고속 신호를 라우팅하면서 선택한 트레이스의 형상이 멀티 기가비트 데이터 레이트에서 실제로 작동할지 궁금해 본 적이 있으신가요? 분명 혼자만이 아닙니다. PCB 설계에서 가장 일반적으로 사용되는 전송 선로 구조는 마이크로스트립 라인이지만, 이 라인은 형상, 재료, 제조 공차에 매우 민감합니다. 깨끗한 아이 다이어그램과 신호 무결성 악몽의 차이는 마이크로스트립 라인 설계가 올바르게 이루어졌는지에 달려 있습니다. 2.4GHz RF 프론트엔드를 설계하든, PCIe Gen4 인터페이스든, 고속 ADC 데이터 패스든 마이크로스트립 라인은 핵심 도구입니다. 외부 레이어에서 접근이 가능하다는 점이 대부분의 설계자가 기본으로 선택하는 이유이지만, 방사, 손실, 환경 민감성에 있어 신중한 공학적 검토가 필요한 트레이드오프가 있습니다. 물리학은 다소 복잡하지만 핵심은 전기장 분포의 균형을 맞추고 실제 보드의 기생 요소에 대한 신호 내구성을 극대화하는 것입니다. 이제 기본적인 전자기 물리학과......