PoP Package (Package on Package) Explained: Architecture, Assembly, and SMT Challenges

10 min

- What Is a PoP Package (Package on Package)?

- Why Use Package on Package (PoP)? Key Advantages in High-Density Electronics

- PoP Package Structure: Logic and Memory Stack Explained

- PoP Package Architecture Types: Standard PoP vs TMV PoP

- Critical SMT Assembly Challenges of PoP Package

- How Advanced SMT Processes Mitigate PoP Assembly Risks

- Design for Assembly (DFA) Guidelines for PoP Packages

- Conclusion

- FAQs

In the race for miniaturization, fitting more processing power into smaller footprints is the ultimate challenge for PCB designers.

Package on Package (PoP) technology answers this by integrating logic and memory vertically, becoming the standard for modern mobile processors. However, this 3D architecture demands advanced SMT assembly capabilities beyond standard fabrication. JLCPCB specializes in the high-precision manufacturing required to master these complex stacks.

This guide covers how PoP packaging works, its key advantages, common assembly challenges, and critical design considerations—helping you quickly decide when a PoP package is the right choice for your application.

What Is a PoP Package (Package on Package)?

Package on Package (PoP) is a vertical circuit integration method where two or more separately tested packages are stacked on top of one another. Unlike System in Package (SiP), which often combines multiple dies inside a single enclosure, PoP typically involves stacking a memory package directly on top of a logic package (CPU or Application Processor).

Why Use Package on Package (PoP)? Key Advantages in High-Density Electronics

Why go through the trouble of stacking BGAs? The benefits of high-speed digital design are undeniable.

1. Signal Integrity Advantages of PoP Packages

In high-speed DDR memory interfaces, trace length is the enemy. Long traces introduce inductance, capacitance, and signal reflection. By stacking the memory directly on the CPU, the signal path is reduced from centimeters to millimeters. This creates a cleaner electrical environment, allowing for the faster clock speeds found in LPDDR4 and LPDDR5 technologies.

2. Known Good Die (KGD) Benefits in PoP Assembly

This is a critical commercial advantage. In System in Package (SiP) solutions, multiple dies are molded together. If one die is bad, the whole expensive module is scrapped. In PoP technology, the Logic and Memory packages are tested, packaged, and burned-in separately. We only stack a "Known Good" memory package onto a "Known Good" logic package, significantly increasing final yield.

3. Supply Chain and Memory Sourcing Flexibility in PoP Packages

Because the memory is distinct from the logic, OEMs can source memory from different vendors (Samsung, Micron, Hynix) without redesigning the logic chip or the motherboard, provided the top-interface standard remains compatible.

PoP Package Structure: Logic and Memory Stack Explained

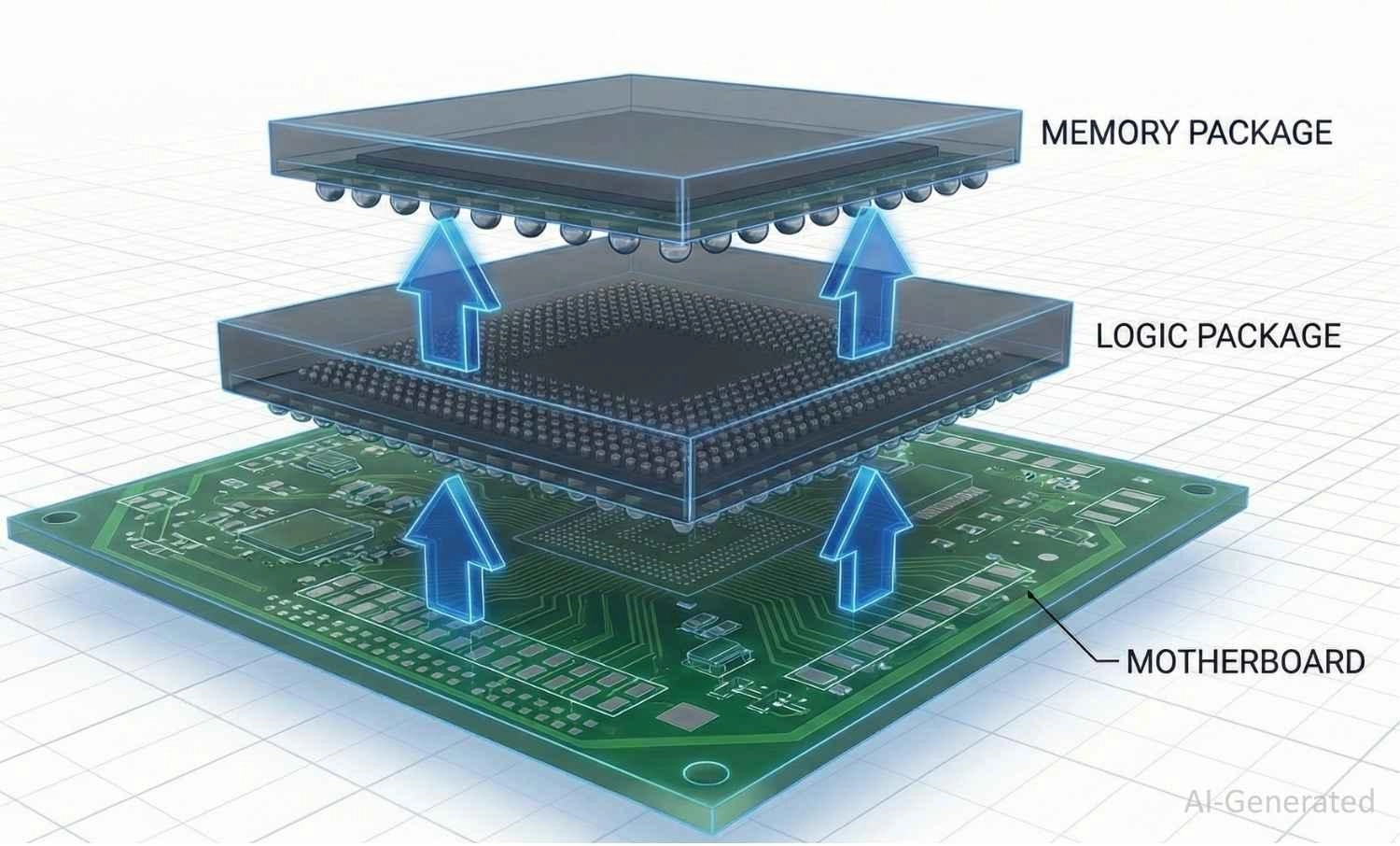

To understand the SMT challenges, we must first understand the physical structure:

1. The Bottom Package (Logic): This contains the application processor. It features a high-density BGA on the bottom to connect to the main motherboard and landing pads on the top surface to accept the memory package.

2. The Top Package (Memory): Usually houses DRAM or Flash memory. It connects to the landing pads of the logic package via a secondary set of solder balls.

3. The Interface: The signals travel vertically through the stack, drastically shortening the distance between the processor and memory.

PoP package structure showing logic and memory stack integration.

PoP Package Architecture Types: Standard PoP vs TMV PoP

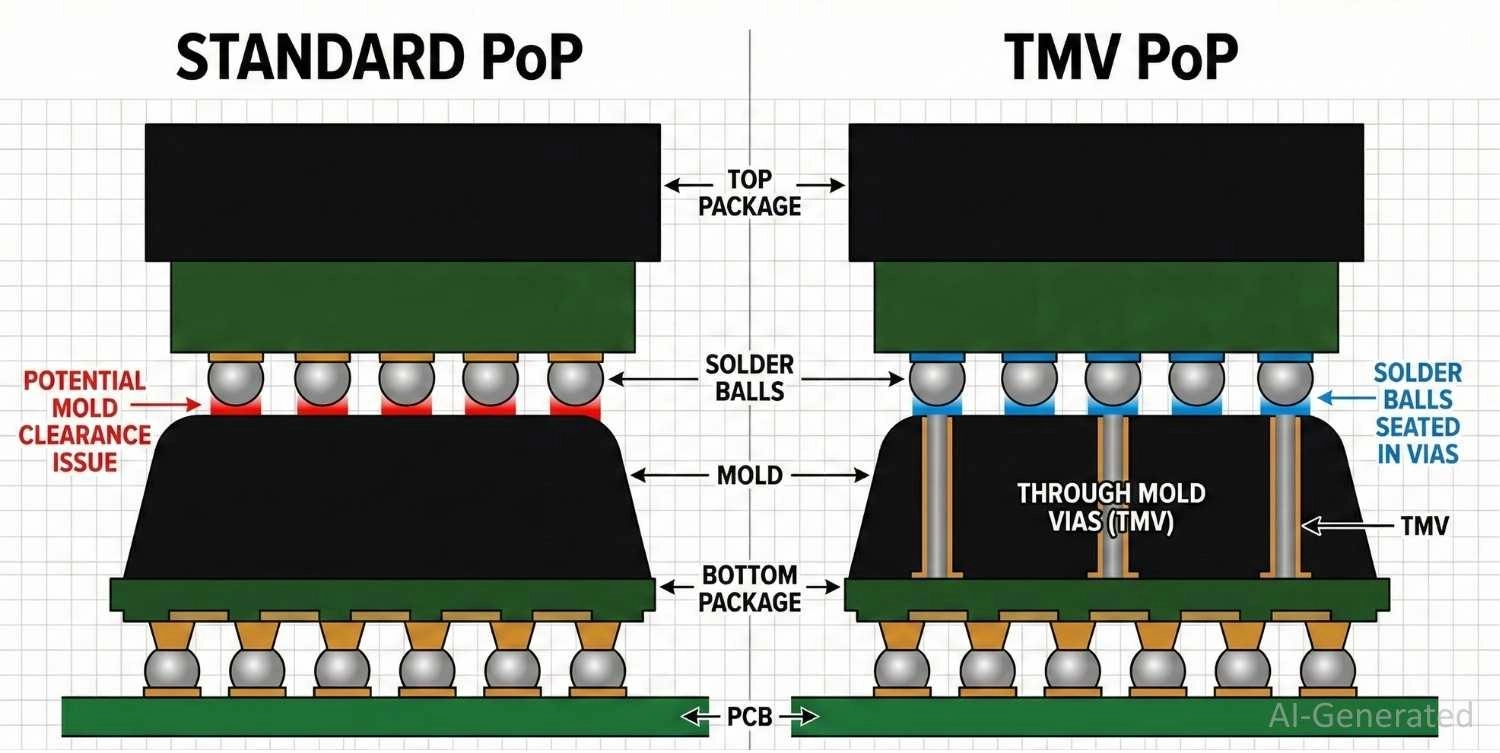

As pin counts increased and devices became thinner, the "Standard" PoP architecture faced limitations. This led to the evolution of Through Mold Via (TMV) technology.

1. Standard PoP Package (Peripheral Ball Stacking)

In the traditional approach, the top memory package sits directly on the mold cap of the bottom logic package. The electrical connection is made via solder balls located on the periphery of the bottom package.

● Limitation: The bottom package must be significantly larger than the top package to accommodate the peripheral solder balls. This limits the die size you can fit inside the bottom package. As pitches shrank below 0.5mm, this method became prone to shorting.

2. Through Mold Via (TMV) PoP Package

To solve the pitch and warpage issues, the industry moved to TMV.

● Mechanism: Instead of placing balls on the edge, vias are created (ablated or molded) through the encapsulation (mold) of the bottom package.

● Technical Advantage: This allows the solder balls of the top package to sit partially inside the mold of the bottom package. It provides a more stable mechanical structure and allows for a larger logic die within the same package footprint. TMV is essential for modern, high-density PoP packages.

Comparison of Standard PoP vs Through Mold Via TMV architecture for high-density SMT assembly.

Critical SMT Assembly Challenges of PoP Package

While PoP solves design problems, it introduces significant challenges for SMT assembly. This is where the difference between a standard assembler and an advanced shop like JLCPCB becomes apparent.

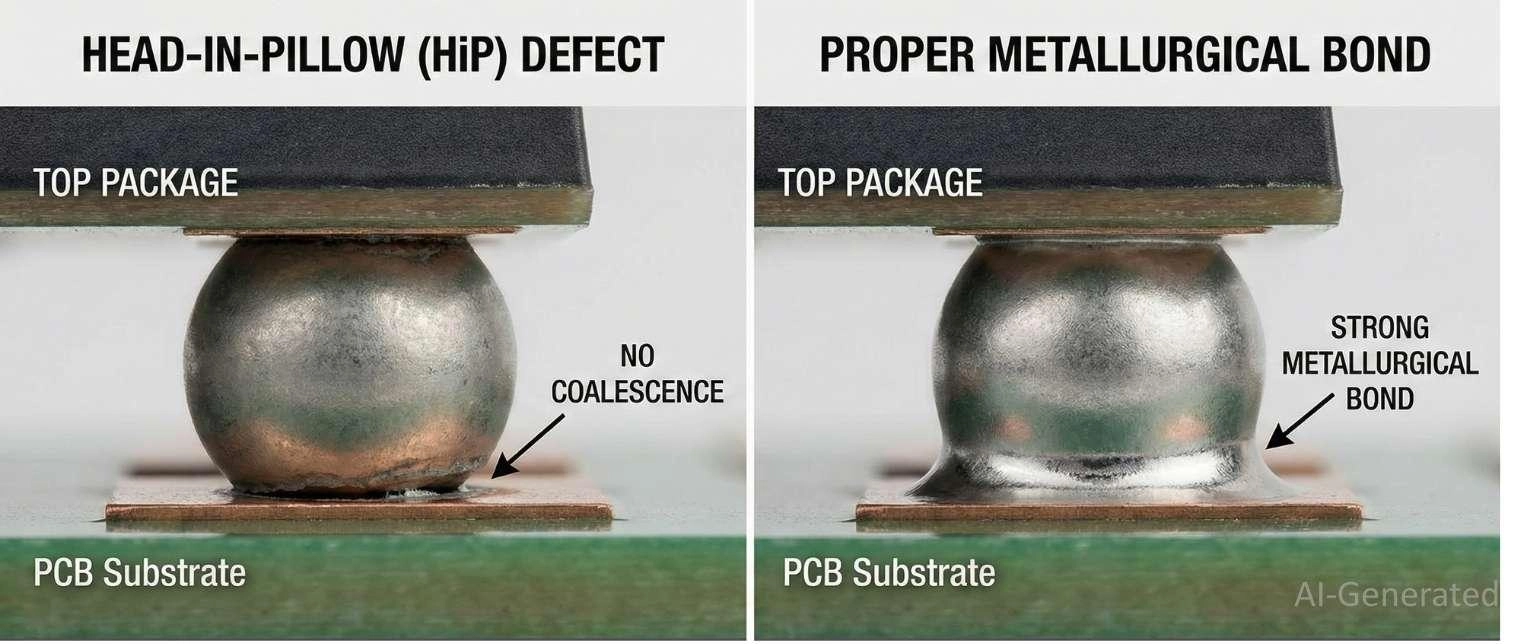

PoP Package Warpage (“Banana Effect”) and Coplanarity Issues

The enemy of PoP assembly is warpage. We are dealing with materials—silicon die, organic substrate, and molding compound—that all have different Coefficients of Thermal Expansion (CTE).

● The Failure Mode: During the reflow oven cycle, as the heat increases, the package expands. The bottom package may warp concave ("smile") or convex ("frown"). If the warpage exceeds the coplanarity tolerance of the solder balls (typically <80 microns), connections will fail.

● Head-in-Pillow (HiP): This occurs when the solder ball melts, but the package has warped away from the pad. The ball creates a shape resembling a head resting on a pillow, making mechanical contact but no metallurgical bond. This creates an intermittent failure that is incredibly difficult to debug.

Head-in-Pillow (HiP) BGA defect caused by warpage in PoP assembly.

Reflow Profile Challenges in PoP Package Assembly

Soldering a PoP stack requires a precise thermal profile.

● The Challenge: You must apply enough heat to melt the solder joints of the top package (which is elevated and insulated) without overheating the bottom package or the PCB components underneath.

● The Solution: This requires reflow ovens with distinct heating zones and strict nitrogen control to prevent oxidation during these extended thermal cycles.

Underfill Requirements and Mechanical Reliability of PoP Packages

Mobile devices are frequently dropped. The solder joints in a PoP stack are rigid and brittle. To pass drop tests, capillary underfill is often injected between the component and the PCB (and sometimes between the two packages). This epoxy distributes mechanical stress, preventing the solder joints from cracking.

How Advanced SMT Processes Mitigate PoP Assembly Risks

Designing a complex PoP board? Don't let assembly defects derail your prototype. At JLCPCB SMT, we utilize advanced nitrogen reflow profiling and 3D Automated Optical Inspection (AOI) to mitigate defects like Head-in-Pillow.

Explore JLCPCB SMT Capabilities

Note: For PCB designers and hardware engineers, the following DFA guidelines are critical to ensure PoP assembly yield and reliability.

Design for Assembly (DFA) Guidelines for PoP Packages

To ensure your PoP package runs smoothly through the JLCPCB PCBA lines, consider these design rules:

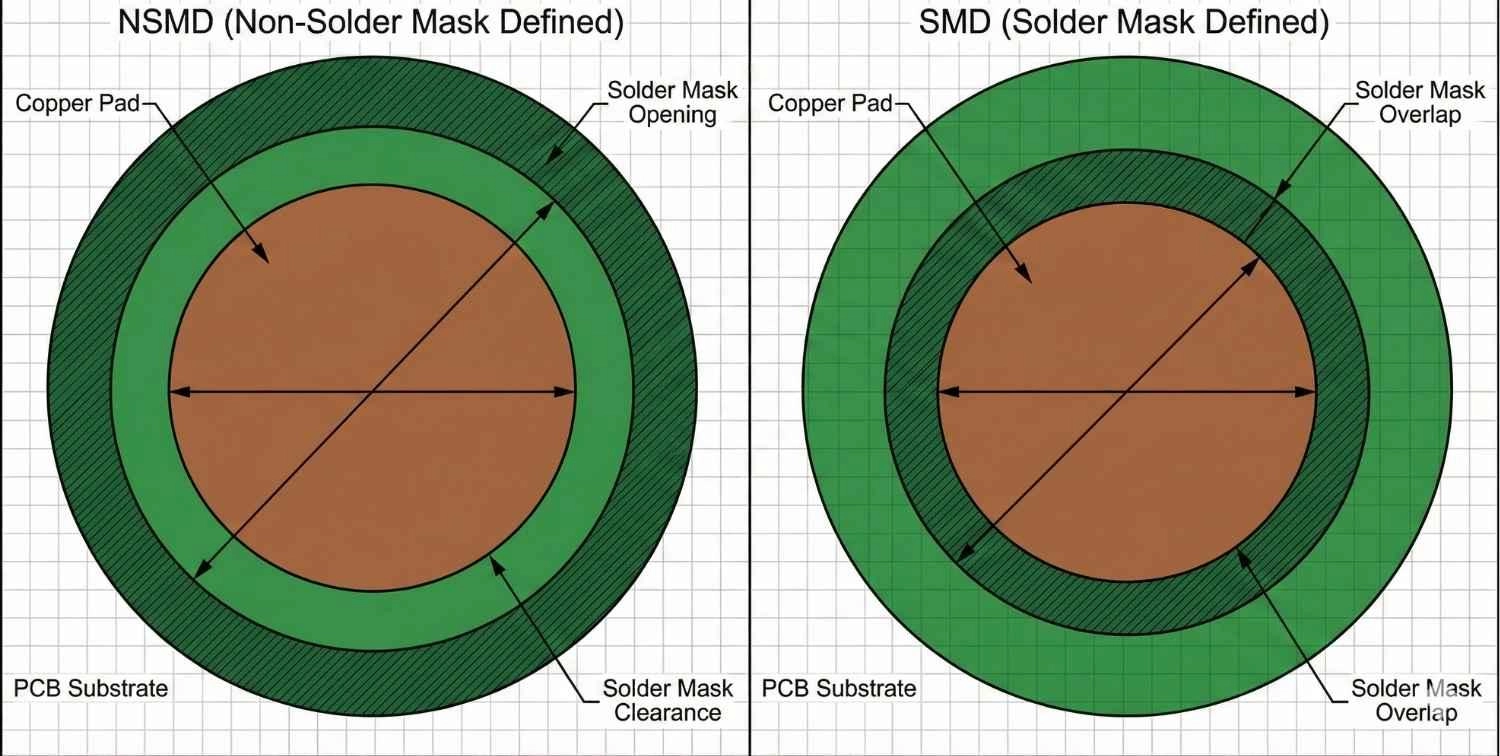

1. PoP Package Pad Design: NSMD is Preferred

For BGA landing pads, Non-Solder Mask Defined (NSMD) pads are generally preferred over Solder Mask Defined (SMD) pads. NSMD pads provide a larger surface area for the solder ball to grip (anchoring on the sides of the copper pad), which improves fatigue life and reduces stress concentration.

Non-Solder Mask Defined (NSMD) vs Solder Mask Defined (SMD) pad geometry for BGA reliability.

2. Stencil Aperture Design for PoP SMT Assembly

The volume of solder paste deposited is critical.

● Too much paste: Causes bridging between the fine-pitch balls.

● Too little paste: Causes open joints or "starved" connections. High-quality, laser-cut, electropolished stencils are mandatory for PoP assembly to ensure consistent release of solder paste.

3. Placement Accuracy and Force Control in PoP Assembly

PoP requires high-end Pick and Place machines. The placement force must be controlled carefully. Too much force can crack the thin silicon die inside the bottom package; too little force might result in the component shifting before reflow.

| Feature | PoP (Package on Package) | SiP (System in Package) | SoC (System on Chip) |

|---|---|---|---|

| Integration | Vertical (Package level) | Horizontal/Vertical (Module) | Silicon (Die level) |

| Flexibility | High (Mix & Match Memory) | Medium | Low (Fixed) |

| Primary Challenge | Warpage & Reflow Height | RF Interference & Shielding | Design Cost & Yield |

| Repairability | Moderate (Top package reworkable) | Low (Replace module) | None (Replace chip) |

Conclusion

Package on Package (PoP) technology is one of the main aspects of modern high-density electronics, as it provides an excellent trade-off between performance, size, and supply chain flexibility. Nevertheless, it is not a technology that is easy to deal with. It requires strict adherence to thermal management, warpage control, and DFA practices, all the way from the start to the end of the manufacturing process.

On the one hand, for engineers, the success of a PoP design depends mainly on the capability of the manufacturer. On the other hand, when it comes to quality, there is no compromise allowed from precise impedance control on the bare board through to the delicate reflow profile management during assembly.

For complex PoP designs, assembly capability is often the deciding factor between success and failure. Are you prepared to realize your high-density designs? If you are using standard BGAs or looking into advanced stacking, JLCPCB provides the industrial-grade manufacturing with the rigor that your projects deserve.

Get Instant Quotes for High-Precision PCBA: Upload your Gerber files today and experience the speed and quality of JLCPCB.

FAQs

Q1: What happens if PoP is assembled without underfill?

Underfill is not always required from the electrical point of view, but it is more or less obligatory for mobile devices to meet drop-test reliability standards. In line with this, mechanical protection is used for brittle solder joints. The stationary industrial applications might cope with corner bonding or edge bonding, but full underfill gives the best mechanical protection for the fragile solder joints.

Q2: What happens if the bottom package fails in a PoP stack?

It is extremely hard and tricky to rework a stack of PoP. The usual procedure is that when the top memory package fails, it can be taken off and replaced with the help of a professional BGA rework station. When, however, there is a failure of the bottom logic package, the usual practice is to do the whole removal of the stack, including the reballing or replacement, because the heat cycles may cause the degradation of the PCB pads.

Q3: What is the difference between PoP and 2.5D packaging?

PoP uses standard organic substrates and solder balls to stack packages vertically (3D). 2.5D technology utilizes a silicon interposer to place dies side by side with extremely fine TSV (Through-Silicon Via) connections. PoP is more cost-effective for mobile consumer electronics, while 2.5D is reserved for ultra-high-performance computing (HPC) due to high manufacturing costs.

Q4: Does PoP packaging cause thermal issues?

Yes, thermal coupling is indeed an issue. The upper memory die can serve as a thermal insulator, retaining the heat from the logic processor that is below it. To counter this problem, engineers must devise thermal paths that are the most effective by utilizing thermal vias in the bottom substrate or placing heat spreaders on top of the memory package to transfer heat away from the stack.

Q5: Why is PoP assembly sensitive to moisture?

PoP packages are extremely thin and susceptible to moisture absorption. If moisture is trapped inside the package encapsulation during the rapid heating of reflow, it expands into steam, causing "popcorning" (delamination) or internal cracking. Unlike standard components, PoP requires strict baking and dry-pack handling (typically MSL 3 or higher) before assembly to prevent catastrophic failure.

Popular Articles

• SMD Capacitor Codes: Identification, Markings, and Polarity

• SMD Resistor Package Sizes: Complete Size Chart, Footprints & How to Choose

• SMD Capacitor Sizes: Complete Size Chart and Selection Tips for PCB Design and Assembly

• How to Solder SMD Components Like a Pro [2026 Updated]

• The Complete Guide to Read SMD Resistor Codes

Keep Learning

Complete SMD Inductor Size Guide: Dimensions, Packages, and PCB Design Tips

SMD inductor size affects far more than PCB real estate. Package dimensions directly influence current handling, saturation behavior, DCR, and EMI characteristics. Picking the wrong package can mean a costly board respin, not just inefficiency. One challenge is that SMD inductor package sizes use multiple naming conventions and the fundamental split between RF chip inductors (compact footprint, high Q-factor) and power inductors (low DCR, magnetic shielding, high saturation current). This guide covers......

The Ultimate Guide to SMD Transistor Package: Sizes, Footprints, Thermal Performance & Selection

Choosing the wrong transistor package, thermal limitations, or excessive PCB area quickly becomes a problem. SMD transistor packages range from compact SC-70 and SOT-523 devices to much larger DPAK and D2PAK power packages, each optimized for different current, thermal, and assembly requirements. This guide compares common SMD transistor package sizes, including SOT-23, SOT-89, SOT-223, SC-70, DPAK, and D2PAK. You'll find nominal dimensions, footprint sizes, thermal characteristics, current capabiliti......

LED Sizes Explained: Complete LED Size Chart, Types, Dimensions, and Applications

LEDs come in multiple package types, and choosing the wrong LED size affects brightness, PCB footprint, thermal performance, and assembly method. Whether you are placing an indicator on a breadboard, designing an LED strip PCB, or specifying a COB module for a spotlight, size is the first decision to get right. This guide covers every major LED size category, through-hole dimensions, SMD package codes, COB module sizes, and the difference between chip size and package size, with a quick-reference char......

SMD Capacitor Codes: Identification, Markings, and Polarity

Identifying SMD capacitor codes is a unique and often confusing challenge. Unlike components with clear, standardized labels, capacitor markings depend entirely on capacitor type, and in most cases, the marking is a complete absence of one. As fundamental components for storing charge, capacitors are essential for every part of an embedded system, from filtering power supply noise (decoupling) and setting oscillator timing to coupling signals between ICs. Correctly identifying them is a critical skill......

Complete SMD Diode Size Guide: Package Dimensions, Charts, and Selection Tips

Picking the wrong SMD diode package usually shows up late, either during layout when footprints mismatch, or during testing when junction heating climbs past safe limits. Package size dictates how much current a diode carries, how efficiently it sheds heat, and whether your assembly line can solder it reliably. This guide details common SMD diode package families (SMA, SMB, SMC, SOD-123, SOD-323, SOD-523, and SOD-923). You will find our comprehensive SMD diode package size chart, layout recommendation......

Diode Type Guide: How to Choose the Right Diode for PCB and Product Design

Modern electronics rely on highly specialized diode types for power conversion, ESD protection, signal detection, and high-frequency switching. Choosing the wrong diode doesn't just reduce efficiency; it also generates excess heat, introduces switching losses, and can even damage sensitive circuits during voltage transients. Choosing the right component ensures a reliable board, whether you are wiring a prototype or scaling to low-volume PCB assembly. In this guide, you'll learn: How do different diod......