デジタル回路のタイミング理解:セットアップ時間、ホールド時間、汚染遅延、クロックスキュー

1 min

- デジタル設計におけるタイミングパラメータ

- 伝搬遅延と汚染遅延

- クロックスキュー(Clock Skew)

- セットアップ時間(Setup Time)

- ホールド時間(Hold Time)

- タイミングパス

- タイミング方程式

- 数値例(単一サイクルパス)

- 違反の原因と対策

- 設計テクニック

- まとめ

本記事は、デジタル回路における伝搬遅延(Propagation Delay)シリーズの第2回です。デジタル回路設計では、必ず満たすべき重要な要素が2つあります。1つ目は機能(Functionality)、2つ目は**タイミング(Timing)**です。前回の記事では基本ブロックについて解説しました。

電子回路において「時間」とはクロックの刻みそのものです。すべてはクロックエッジを基準に動作しており、動作周波数や処理速度もこのクロックによって決まります。マイクロコントローラ、FPGA、ASICを扱う場合、回路を正しく動作させるためにはタイミング制約を満たす必要があります。本記事では、設計時に考慮すべき主要なタイミング制約について解説します。

本ガイドでは以下の基礎項目を扱います:

- セットアップ時間(Setup Time)

- ホールド時間(Hold Time)

- 汚染遅延(最小遅延 / Contamination Delay)

- クロックスキュー(Clock Skew)

さらに、それらがタイミング方程式や実設計でどのように相互作用するかも説明します。

デジタル設計におけるタイミングパラメータ

組み合わせ回路ブロックでは、次の2つの遅延指標が重要です。

- Tpd(最大伝搬遅延) 組み合わせ回路を通過する最悪ケース(最長)の遅延。セットアップチェックで使用されます。

- Tcd(最小汚染遅延) 組み合わせ回路を通過する最短遅延。ホールドチェックで使用されます。

- クロック周期(Tclk) 連続するクロックエッジ間の時間。

伝搬遅延と汚染遅延

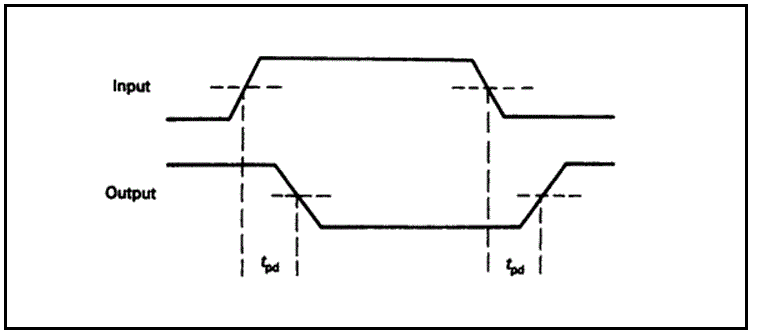

● 伝搬遅延(Tpd, max)

ゲートやロジックブロックを通過する最長遅延。

セットアップ時間の検証で使用されます。最も遅く到達するデータがセットアップ要件を満たす必要があるためです。

● 汚染遅延(Tcd, min)

ゲートやロジックブロックを通過する最短遅延。

ホールド時間の検証で使用されます。最も早く変化するデータを考慮する必要があるためです。

クロックスキュー(Clock Skew)

クロックがソースフリップフロップとキャプチャフリップフロップに到達する時間差を指します。主な原因は以下の通りです:

- クロックツリーの不均衡

- 配線差異

- バッファ挿入

- 合成/CTS選択

- ローカルクロックゲーティング

- PLLやバッファのジッタ

- 正のスキュー:キャプチャ側クロックが遅れて到達

- 負のスキュー:キャプチャ側クロックが早く到達

設計上、セットアップを緩和する目的で意図的にスキューを導入することもあります(Useful Skew)。

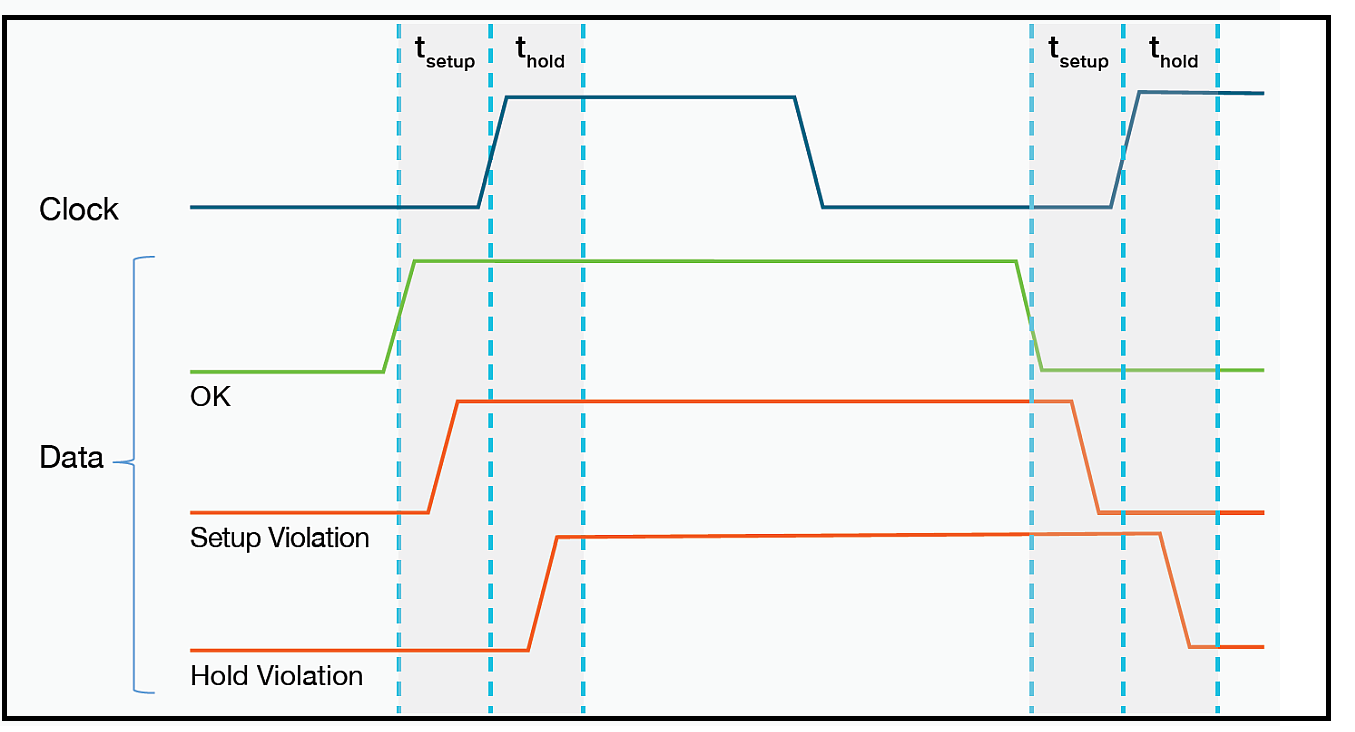

セットアップ時間(Setup Time)

セットアップ時間(Tsu)は、アクティブクロックエッジの前にデータが安定していなければならない最小時間です。

データ到達が遅すぎると、キャプチャフリップフロップが誤った値をサンプリングする可能性があります。最悪の場合、メタステーブル状態に陥ることもあります。

セットアップ違反は主に**最大伝搬遅延(Tpd)**が大きすぎる場合に発生します。

ホールド時間(Hold Time)

ホールド時間(Thold)は、クロックエッジの後にデータが安定していなければならない最小時間です。

データが早く変化しすぎると、キャプチャフリップフロップが不正な値をサンプリングする可能性があります。

最も早い到達時間は:

Tcq + Tcd

これがホールド時間を満たさなければなりません。

タイミングパス

典型的な同期タイミングパス:

Launch FF → Tcq → 組み合わせ回路 → Tpd/Tcd → Capture FF → Setup/Holdチェック

- Launchイベント:フリップフロップAが新しいデータを出力

- Captureイベント:フリップフロップBが次クロックエッジでデータを取得

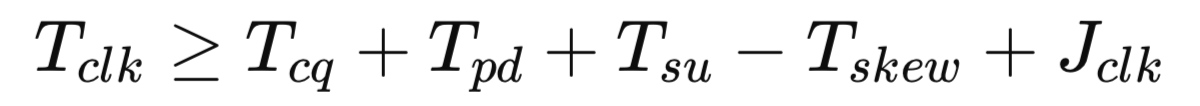

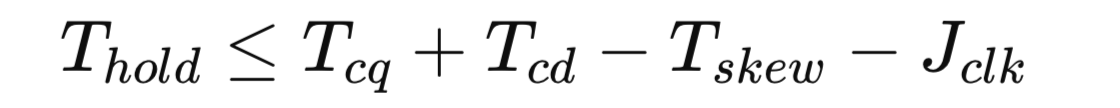

タイミング方程式

● セットアップ条件

● ホールド条件

※Jclkはクロックジッタ。安全マージンを減少させる要素として扱います。

数値例(単一サイクルパス)

与えられた値:

- Tclk = 5.0 ns

- Tskew = +0.10 ns

- Tcq = 0.12 ns

- Tpd = 2.80 ns

- Tsu = 0.08 ns

- Tcd = 0.02 ns

- Thold = 0.05 ns

セットアップチェック

必要時間 = 0.12 + 2.80 + 0.08 − 0.10 = 2.90 ns

Slack = 5.00 − 2.90 = 2.10 ns → PASS

ホールドチェック

許容時間 = 0.12 + 0.02 − 0.10 = 0.04 ns

Slack = 0.04 − 0.05 = −0.01 ns → 10psのホールド違反

実設計ではこのように、セットアップは余裕があってもホールド違反が発生することは珍しくありません。

違反の原因と対策

セットアップ違反対策

- パイプライン挿入

- ロジック深さ削減

- 高ドライブセル使用

- 配線最適化

- 電圧改善

ホールド違反対策

- バッファ挿入

- 意図的な遅延追加

- 配線を長くする

- マルチサイクルパス設定

設計テクニック

● Useful Skew

セットアップを緩和するために意図的にスキューを導入。

● マルチサイクルパス

複数サイクルを許容できるパスはSTAで適切に制約設定。

まとめ

本記事では、セットアップ時間とホールド時間を中心に、汚染遅延やクロックスキューとの関係を詳しく解説しました。

- セットアップは最大遅延で決まる

- ホールドは最小遅延で決まる

- 機能だけでなくタイミングも同じくらい重要

デジタル回路設計では、機能とタイミングの両立が不可欠です。本シリーズでは今後もタイミング関連の高度なテーマを扱っていきます。

学び続ける

PCB ビアとは何か、そしてどのタイプを選ぶべきか?

プリント回路基板(PCB)の設計は、電子製品開発において極めて重要な要素です。PCBは電子部品を秩序正しくコンパクトに配置し、効率的な信号伝達を可能にするとともに、電気的な干渉のリスクを最小限に抑えます。PCB設計において欠かせない要素の1つがビア(via)です。ビアは基板に小さく開けられた穴で、基板の異なる層間を電気的に接続する役割を果たします。 本記事では、PCBビアの概要を包括的に解説し、種類、設計上の考慮事項、アプリケーションについて説明します。また、適切なビアを選択することが製品の性能と信頼性に与える影響についても議論します。 ビアとは? ビアは、PCBに開けられた小さな穴で、基板の異なる層間を接続します。ビアの内壁は銅などの導電性材料でコーティングされており、穴を通じて電流が流れ、層間の接続を確立します。ビアは多層PCB設計において不可欠であり、異なる層間の電気的・熱的な接続を提供します。 ビアは基板の全面を貫通してすべての層を接続する場合もあれば、基板の一部のみを貫通して数層のみを接続する場合もあります。ビアのサイズや形状は用途や設計要件によって異なり、円形以外の形状もあり、直径は数......

デジタル回路のタイミング理解:セットアップ時間、ホールド時間、汚染遅延、クロックスキュー

本記事は、デジタル回路における伝搬遅延(Propagation Delay)シリーズの第2回です。デジタル回路設計では、必ず満たすべき重要な要素が2つあります。1つ目は機能(Functionality)、2つ目は**タイミング(Timing)**です。前回の記事では基本ブロックについて解説しました。 電子回路において「時間」とはクロックの刻みそのものです。すべてはクロックエッジを基準に動作しており、動作周波数や処理速度もこのクロックによって決まります。マイクロコントローラ、FPGA、ASICを扱う場合、回路を正しく動作させるためにはタイミング制約を満たす必要があります。本記事では、設計時に考慮すべき主要なタイミング制約について解説します。 本ガイドでは以下の基礎項目を扱います: セットアップ時間(Setup Time) ホールド時間(Hold Time) 汚染遅延(最小遅延 / Contamination Delay) クロックスキュー(Clock Skew) さらに、それらがタイミング方程式や実設計でどのように相互作用するかも説明します。 デジタル設計におけるタイミングパラメータ 組み合わせ回路......

PCB基板の種類:仕様と用途を網羅した究極リファレンス

プリント基板(PCB)は、積層された絶縁材料と導電材料から構成され、複数の電子デバイスを接続します。PCBは、ガラス繊維とエポキシの層状複合体に銅パターンをエッチングしたものと考えることができます。これらは信号および電力の電気的導体および経路として機能します。PCBは、単純なもの(導電層が1層)、両面(導電層が2層)、または複雑なもの(3層以上の導電層)に分類され、小さなハードウェア上に多数の回路経路を実現します。IPCによると、PCBとは、電子アセンブリのための電気回路を形成するために、導電材料と非導電材料を積層したものです。 IPC公式定義+レイヤー構造 実務的な定義は明確です。PCBは誘電体層と金属銅箔層が交互に積層された構造で構成されます。銅層にはトレース、プレーン、パッド、ビアのパターンがあり、部品を接続します。典型的な4層PCBのスタックアップは次のようになります。 銅層 – プリプレグまたはコア – 銅 – コア – 銅 すべての層は接着されています。樹脂/ガラス基材は機械的強度と電気絶縁性を提供します。IPC-2221およびIPC-4101規格は、スタックアップ形状および材料特性を......

PCBホルダーの基本:回路基板の安定性向上のヒント

回路基板ホルダー、別名PCBホルダーは、PCBをしっかり固定するために設計された機械的治具です。基板を固定することで、はんだ付け、はんだ除去、テストなどの作業中に基板が動かないようにします。このハンズフリーサポートは、単なる利便性向上だけでなく、繊細な電子作業における安全性と精度も高めます。良質なPCBホルダーは安定性を確保し、基板を確実な位置に保持します。また、組立工程全体で部品を正確に配置するための位置合わせにも役立ちます。要するに、適切なホルダーは事故や不安定なはんだ接合を防ぐ「第三の手」です。 日常使用に適したPCBホルダーの条件 日常使用では、耐久性があり、調整が容易なホルダーが必要です。主な特徴は次の通りです。 高温対応材料の使用: 高温プラスチック製のホルダーは、はんだごての熱による変形がありません。多くのホルダーはこの理由から耐熱材料で作られています。 安定した調整可能なクランプ: クランプは基板の端部を確実に保持し、曲がりが生じないようにする必要があります。また、クランプはさまざまなサイズのPCBに対応できる十分な可動範囲を持つべきです。ほとんどのホルダーには、使用中に基板を傷つ......

PCBにおけるスタンドオフスペーサーの統合:機械的信頼性と性能を確保するための重要ポイント

スタンドオフスペーサーとは、基本的に回路基板を支えるための小さな支柱部品です。これらは単なる小さなパーツではなく、PCBアセンブリにおいて重要な役割を担います。スタンドオフはPCBをわずかに持ち上げることで、適切な空気の流れを確保します。その結果、より良い絶縁性と機械的サポートが実現されます。スタンドオフは基板を安定させ、他の部品との接触を防ぎます。適切なスタンドオフを選択することで、機器が正常に動作するか、故障や分解につながるかが大きく変わります。 また、部品の下に空気が循環する空間を作り出すことができ、これは合理的な設計判断です。密集した構成において適切な間隔を維持することは、冷却と安全性の両方にとって非常に重要です。 確実な固定と耐振動性の確保 金属製スタンドオフは、産業用コントローラやサーバー筐体間の移動による曲げや破損から回路基板を安定させ、支えます。大型の回路基板に対しても、過度な動きによる曲がりを防ぐため金属サポートを提供します。 ファスナー(主にネジ)にはワッシャーが組み込まれていることが多く、締めすぎによる損傷を防ぐ追加保護を提供します。回路基板を適切に固定するには、ファスナーと......

PCBレイヤー徹底解説:スマートなスタックアップ設計・規格・設計手法で高性能基板を実現

PCB(プリント基板)は、銅箔と絶縁層を積み重ねて構成される“サンドイッチ構造”です。それぞれのPCBレイヤーには明確な役割があります。信号(部品間を接続する配線パターン)を担う層もあれば、電源やグラウンドとして機能する全面プレーン層もあります。 PCBレイヤーは、建物のフロアのようなものと考えると分かりやすいでしょう。ある階はオフィス(信号層)、別の階は倉庫(電源・グラウンド層)というイメージです。レイヤー数は設計の複雑さによって異なり、単層から高度な電子機器では十数層以上になることもあります。 本記事では、効果的なレイヤースタックアップの構築方法、EMI(電磁干渉)の最小化、信号完全性(Signal Integrity)の向上方法について解説します。すべてはレイアウト設計と適切な配置にかかっています。 単層PCBと多層PCBにおけるレイヤー定義 単層PCB 最も基本的なのが単層PCBです。片面のみに銅箔があり、製造コストが低いのが特徴です。LEDドライバなどの低コスト回路に適しています。 両面PCB 標準的なのは両面PCBです。表裏両面に銅箔があり、配線の自由度が大幅に向上します。両層は「ビア......