Differentielle Leiterpaare auf Leiterplatten: Best Practices für Leitungsführung, Impedanzanpassung und Signalintegrität

7 min

- Einführung: Die Bedeutung von Differentialpaaren in Hochgeschwindigkeits-Leiterplatten

- Wichtige Vorteile und gängige Standards für Differentialpaare

- Wesentliche Designregeln für zuverlässige Differentialpaare

- Fortgeschrittene Routing-Techniken und Signalintegritäts-Praktiken

- Häufige Herausforderungen beim Differentialpaar-Design und deren Lösung

- Fazit

- FAQ: Häufige Fragen zu Differentialpaaren

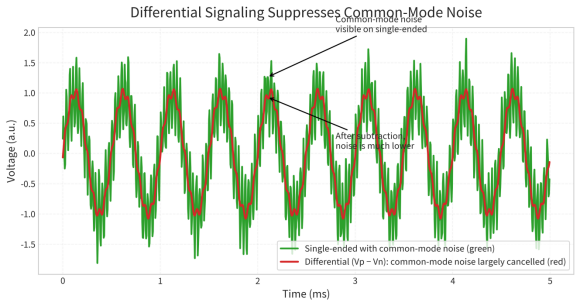

Hochgeschwindigkeits-Digitalentwürfe verlassen sich zunehmend auf Differentialpaare, um Daten zuverlässig mit Raten von mehreren Gbps bis zu Dutzenden Gbps zu übertragen. Diese gepaarten Leitungen führen Signale gleicher Amplitude, aber entgegengesetzter Polarität, wodurch Empfänger Gleichtaktstörungen unterdrücken und das Differenzsignal erhalten können. Ingenieure verwenden Differentialpaare für Schnittstellen wie USB, HDMI, PCIe und Ethernet, da sie eine überlegene Störfestigkeit und geringere EMI im Vergleich zu einzelnen Leitungen bieten.

Einführung: Die Bedeutung von Differentialpaaren in Hochgeschwindigkeits-Leiterplatten

Grundlagen der Differenzsignalübertragung

Differentialpaare bestehen aus zwei komplementären Leitungen (positiv und negativ), die Signale mit entgegengesetzter Polarität übertragen. Der Empfänger subtrahiert das Negative vom Positiven, um die ursprünglichen Daten wiederherzustellen. Diese Subtraktion hebt Störungen auf, die auf beiden Leitungen gleichermaßen auftreten, etwa durch Spannungsschwankungen oder externe Störquellen. In der Leiterplatte ist der Schlüsselparameter der differentielle Wellenwiderstand – typischerweise 90–100 Ohm je nach Standard –, der auf dem gesamten Weg konstant bleiben muss, um Reflexionen zu vermeiden.

Warum Differentialpaare heute unverzichtbar sind

Die Datenraten moderner Geräte sind dramatisch gestiegen, von 480 Mbps bei USB 2.0 bis zu 20 Gbps pro Lane bei PCIe 5.0. Einzelne Signale haben bei diesen Geschwindigkeiten Probleme mit Störungen und Skew, was zu Bitfehlern führt. Differentialpaare tolerieren längere Leitungslängen und rauere Umgebungen und strahlen weniger EMI ab. Sie sind Standard in Unterhaltungselektronik, Automotive-Infotainment und Rechenzentren, wo die Signalintegrität direkt die Leistung beeinflusst.

Wichtige Vorteile und gängige Standards für Differentialpaare

Vorteile gegenüber einzelnen Signalleitungen

Differentialpaare bieten mehrere praktische Vorteile. Sie liefern eine ausgezeichnete Gleichtaktunterdrückung, oft 20–40 dB besser als einzelne Leitungen, was die Anfälligkeit für Ground-Bounce und Übersprechen reduziert. EMI-Emissionen sinken, da die entgegengesetzten Ströme Magnetfelder aufheben. Rückflussströme bleiben zwischen dem Paar und seiner Referenzebene eingeschlossen, was die Schleifenfläche minimiert. In störungsbehafteten Umgebungen wie Automotive- oder Industriesystemen führen diese Vorteile zu niedrigeren Bitfehlerraten und robusteren Verbindungen.

Beliebte Standards und typische Impedanzanforderungen

Die meisten Hochgeschwindigkeitsschnittstellen spezifizieren Differentialpaare mit engen Impedanztoleranzen. Häufige Beispiele sind:

| Standard | Typischer differentieller Wellenwiderstand | Datenrate Beispiel | Hinweise |

| USB 2.0/3.0 | 90 Ω ±15% | 480 Mbps / 5 Gbps | Full-speed und SuperSpeed |

| HDMI 1.4/2.0 | 100 Ω ±10% | Bis zu 18 Gbps | TMDS-Paare |

| PCIe 3.0/4.0 | 100 Ω ±10% | 8–16 GT/s pro Lane | Hohe Toleranz für Reflexionen |

| 1000BASE-T Ethernet | 100 Ω ±10% | 1 Gbps | Twisted-Pair-Emulation auf der Leiterplatte |

Tabelle 1: Gängige Differentialpaar-Standards und Impedanz-Ziele.

Diese Werte stammen aus Schnittstellen-Spezifikationen und erfordern kontrollierte Dielektrika und Leitungsgeometrie während der Fertigung.

Wesentliche Designregeln für zuverlässige Differentialpaare

Impedanzkontrolle, Breite, Abstand und Längenanpassung

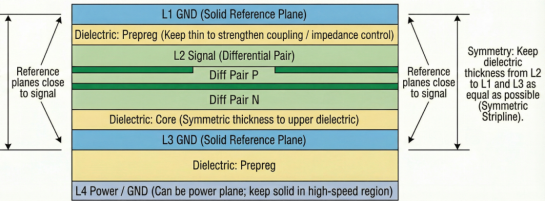

Der differentielle Wellenwiderstand wird aus Leitungsbreite (W), Abstand (S), Höhe zur Referenzebene (H) und Dielektrizitätskonstante (Er) berechnet. Für ein typisches 100-Ω-Paar auf FR-4 eignen sich Breiten von 4–6 mil mit Abstand 5–8 mil und Prepeg-Dicke 4–6 mil. Feldlöser wie Saturn PCB Toolkit oder integrierte Rechner in Altium/KiCad liefern präzise Werte basierend auf Stackup. Variationen durch Ätzen oder Dielektrika können die Impedanz um 5–10% verschieben, geben Sie daher Toleranzen in Fertigungsnotizen an. Längenanpassung begrenzt Intra-Pair-Skew auf 5–15 ps (je nach Anstiegszeit) – verwenden Sie Akkordeon- oder Sägezahn-Muster auf der längeren Leitung, halten Sie die Amplitude gering (<3× Breite), um zusätzliche Induktivität oder Kapazität zu vermeiden.

Referenzebenen, Rückflusswege und Lagenwahl

Eine durchgehende Referenzebene (vorzugsweise Masse) direkt neben dem Paar ist essentiell für stabilen Wellenwiderstand und niedrige Induktivität des Rückflusses. Aufgeteilte Ebenen zwingen Rückflussströme zu Umwegen und erzeugen Gleichtaktstörungen. In Mehrfachlagen-Designs bevorzugen Sie Innenlagen zur Abschirmung gegen externe Störungen, stellen Sie aber sicher, dass der Stackup symmetrisch ist, um Verwerfungen während der Laminierung zu kontrollieren. Bei hoher Lagenzahl wechseln Sie Signale und Ebenen, um mehrere Referenzen zu bieten. Stich-Vias alle 5–10 mm um den Paar-Umfang verbinden Ebenen über Lagen hinweg.

Fortgeschrittene Routing-Techniken und Signalintegritäts-Praktiken

Kopplungsstrategien, Via-Behandlung und Übersprechen-Reduktion

Starke Kopplung (S ≈ W) maximiert Gleichtaktunterdrückung, senkt aber den Wellenwiderstand; schwache Kopplung erhöht den Wellenwiderstand und erleichtert Anpassung. Routen Sie Paare mit konstantem Abstand und vermeiden Sie scharfe Biegungen – verwenden Sie 45-Grad-Winkel oder Bögen mit Radius >3× Breite. Für Vias minimieren Sie Stubs durch Rückbohren oder blind/buried Vias; platzieren Sie Paar-Vias symmetrisch und umgeben Sie sie mit Masse-Vias (4–6 pro Paar), um Abschirmung zu wahren. Halten Sie Paare mindestens 5H (Höhe zur Ebene) von Störern entfernt, um Fern-End-Übersprechen unter -40 dB zu begrenzen.

Simulationswerkzeuge und Fertigungsaspekte

HyperLynx oder SIwave für Pre- und Post-Layout-Simulation zeigen Augenöffnung oder Reflexionen frühzeitig. TDR-Tests verifizieren Impedanzkontinuität. Fertigungsfaktoren wie Kupferrauheit (low-profile-Folie bevorzugt), Lötstopphöhe und Ätz-Uniformität beeinflussen Verlust und Skew. Kontrollierte Prozesse erreichen ±8–10% Impedanzgenauigkeit, mit Test-Coupons auf Panels zur Verifizierung. DFM-Regeln umfassen das Vermeiden von Säurefallen bei engem Abstand und die Sicherstellung der minimalen Bohrung-zu-Kupfer-Distanz für zuverlässige Plattierung.

Häufige Herausforderungen beim Differentialpaar-Design und deren Lösung

Impedanzdiskontinuitäten, Skew und EMI-Probleme

Biegungen, Stecker oder Lagenwechsel erzeugen Impedanzabfälle, die Reflexionen verursachen und Augenöffnungen verschlechtern. Übermäßiger Intra-Pair-Skew wandelt Differenz- in Gleichtakt um und erhöht EMI. Lösungen umfassen allmähliche Übergänge, enge Längentoleranzen (<0,1 mm für >5 Gbps) und Abschirmung durch Masseflächen oder Vias.

Rolle professioneller Fertigung bei der Toleranzbehebung

Ätzvariation und dielektrische Ungleichmäßigkeit können die Impedanz um 10–15% verschieben. Professionelle Hersteller verwenden Laser-Direkt-Imaging für präzise Strukturierung, kontrollierten Prepeg-Fluss und Impedanz-Coupon-Tests, um ±5–10% Genauigkeit zu halten. Sie optimieren auch den Stackup für verlustarme Materialien und geben frühes DFM-Feedback zur Via-Struktur oder Abstandsrealisierbarkeit.

Fazit

Differentialpaare sind kritisch, wenn Datenraten 1 Gbps überschreiten, Störabstände kleiner werden oder EMI-Konformität gefordert ist – häufig in modernen Schnittstellen wie USB-C, PCIe und hochauflösender Videoübertragung. Richtige Implementierung sorgt für offene Augen, niedrige BER und Zertifizierung.

Für zuverlässige Ergebnisse arbeiten Sie mit einem Hersteller, der Erfahrung mit Hochgeschwindigkeits-Leiterplatten hat. JLCPCB bietet präzise Impedanzkontrolle (±10% Standard, enger auf Anfrage), Multilayer- und HDI-Unterstützung für dichtes Routing sowie Quick-Turn-Prototyping, um Signalintegrität früh zu validieren. Ihr Online-Rechner und DFM-Checks helfen, Differentialpaar-Parameter vor der Produktion zu verfeinern. Laden Sie Ihr Design bei jlcpcb.com hoch, um sofort ein Angebot und Fertigung zu erhalten, die anspruchsvolle Hochgeschwindigkeits-Anforderungen erfüllt.

FAQ: Häufige Fragen zu Differentialpaaren

F1: Was ist der Hauptunterschied zwischen Differenz- und Einzelsignalübertragung?

A: Differenzielle Übertragung verwendet zwei komplementäre Leitungen, um Gleichtaktstörungen zu unterdrücken, und bietet bessere Immunität (20–40 dB) sowie geringere EMI als einzelne Signalleitungen, die auf eine einzelne Leitung und Masse-Referenz angewiesen sind.

F2: Wie eng sollte die Längenanpassung bei Differentialpaaren sein?

A: Halten Sie Intra-Pair-Skew unter 5–15 ps (oder <0,1 mm für >5 Gbps), um Zeitfehler und Moduskonversion zu verhindern – verwenden Sie Serpentinen auf der längeren Leitung.

F3: Warum ist eine durchgehende Referenzebene für Differentialpaare kritisch?

A: Sie garantiert konstanten Wellenwiderstand, niedrig-induktive Rückflusswege und Abschirmung; aufgeteilte Ebenen zwingen Ströme zu Umwegen und erzeugen Störungen und Diskontinuitäten.

F4: Kann ich Differentialpaare auf äußeren Lagen routen?

A: Möglich, aber nicht ideal – Innenlagen bieten bessere Abschirmung und Impedanzstabilität; äußere Lagen erhöhen die Anfälligkeit für externe Störungen und erfordern zusätzliche Abschirmung.

Beliebte Artikel

Weiterlernen

Wie man die Impedanz eines Schaltkreises bestimmt: Wichtige Fakten und PCB-Anwendungen

Die Bestimmung der Impedanz eines Schaltkreises ist entscheidend für die Analyse des Verhaltens und die Optimierung der Leistung in Hochgeschwindigkeits- und HF-Designs. Impedanz (im Gegensatz zum einfachen Widerstand) umfasst sowohl Widerstand als auch Reaktanz und ist daher im PCB-Design und in der PCBA-Fertigung unerlässlich. In diesem Artikel erkunden wir die Impedanzformel, Impedanzanpassung, Mikrostreifen-Berechnungen und wie JLCPCBs kostenloser Impedanzrechner Designern hilft, zuverlässige Erge......

Verständnis von DC-5-V-Eingang im PCB-Design: Wichtige Überlegungen

Die DC-5-V-Eingangsspannung ist ein kritischer Aspekt des PCB-Designs, der Spannungsregelung und Kompatibilität für elektronische Projekte sicherstellt. In diesem Artikel erkunden wir die Bedeutung der DC-5-V-Eingang, die Faktoren, die ihre Anforderungen beeinflussen, Best Practices für das PCB-Design mit DC-5-V-Eingangskompatibilität, Test- und Validierungstechniken, Anwendungen in der Praxis und sogar, wie man eine 5-V-Stromversorgung auf einer PCB realisiert. Durch das Verständnis der Wichtigkeit d......

Harmonie im Mixed-Signal-PCB-Design erreichen

In der elektronischen Welt ist es heute aufgrund von Veränderungen üblich, analoge und digitale Bauteile auf einer Platine zu mischen. Mixed-Signal-PCB-Design steht für eine harmonische Verbindung von analoger und digitaler Welt und eröffnet eine Vielzahl von Möglichkeiten für anspruchsvolle elektronische Geräte. Dieser Blogbeitrag behandelt das Thema Mixed-Signal-PCB-Design. Er beleuchtet die Herausforderungen, Best Practices und wichtigen Faktoren für eine optimale Leistung. Das Wesen des Mixed-Sign......

Einsteigerleitfaden zur Impedanzkontrolle in Leiterplatten

Wenn ein digitales Signal von einem Punkt zum anderen übertragen wird, verursacht es eine Zustandsänderung der Signalleitung. Diese Änderung kann als elektromagnetische Welle verstanden werden, die sich durch den Schaltkreis bewegt. Reflexion tritt auf, wenn diese Welle auf eine Grenze zwischen verschiedenen Medien trifft. An dieser Grenze setzt sich ein Teil der Wellenenergie als Signal fort, während der Rest reflektiert wird. Dieser Vorgang wiederholt sich, bis die Energie entweder vom Schaltkreis a......

Reflexionsregel-Rechner für Impedanzanpassung

Wann immer ein Signal digital von einem Punkt zum anderen gesendet wird, ändert es den Zustand einer Signalleitung. Die Zustandsänderung des Signals kann als elektromagnetische Welle beschrieben werden, während es sich durch den Schaltkreis bewegt. Reflexion tritt auf, wenn eine elektromagnetische Welle auf eine Grenze zwischen zwei Medien stößt. Beim Auftreffen auf die Grenze wird ein Teil der Energie als Signal übertragen und ein Teil reflektiert. Dieser Vorgang wiederholt sich unendlich oft, bis di......

Ein praktischer Leitfaden zur Signalintegrität beim Entwurf hochgeschwindigkeitsfähiger starrer Leiterplatten

Wir verwenden den Begriff Signalintegrität oft – was ist das eigentlich genau? Hängt es mit Signalparametern oder Systemparametern zusammen? Ganz einfach: Wenn ein Signal durch einen Draht oder eine Übertragungsleitung läuft, verändern sich einige Parameter zwischen Sender und Empfänger. Bei Hochgeschwindigkeitssignalen ist der Verlust noch größer, was zu Datenverlust und Signalverfälschung führen kann. Welche Art von Signal wird gestört und wie verändert es sich? Wir haben die 4 Hauptursachen erklärt......