Pares Diferenciais em PCBs: Melhores Práticas para Roteamento, Controle de Impedância e Integridade do Sinal

8 min

- Introdução: A Importância dos Pares Diferenciais em PCBs de Alta Velocidade

- Principais Vantagens e Padrões Comuns para Pares Diferenciais

- Regras Essenciais de Design para Pares Diferenciais Confiáveis

- Técnicas Avançadas de Roteamento e Práticas de Integridade de Sinal

- Desafios Comuns no Design de Pares Diferenciais e Como Superá-los

- Conclusão

- FAQ: Perguntas Comuns Sobre Pares Diferenciais

Projetos digitais de alta velocidade dependem cada vez mais de pares diferenciais para transmitir dados de forma confiável em taxas de vários Gbps a dezenas de Gbps. Esses trilhos emparelhados transportam sinais de magnitude igual, mas polaridade oposta, permitindo que os receptores rejeitem ruído de modo comum enquanto preservam o sinal diferencial. Engenheiros usam pares diferenciais para interfaces como USB, HDMI, PCIe e Ethernet porque oferecem imunidade superior ao ruído e EMI reduzida em comparação com trilhos single-ended.

Introdução: A Importância dos Pares Diferenciais em PCBs de Alta Velocidade

Fundamentos da Transmissão Diferencial

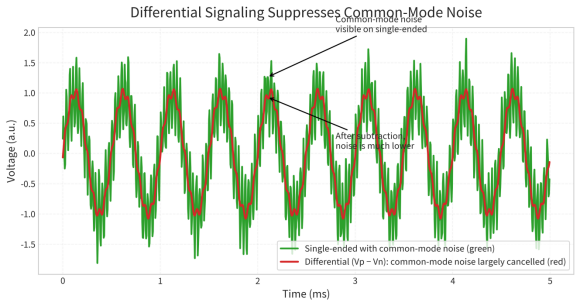

Pares diferenciais consistem em dois trilhos complementares (positivo e negativo) que propagam sinais com polaridades opostas. O receptor subtrai o negativo do positivo para recuperar os dados originais. Essa subtração cancela o ruído captado igualmente em ambos os trilhos, como flutuações da fonte de alimentação ou interferência externa. Em termos de PCB, o parâmetro-chave é a impedância diferencial — tipicamente 90–100 ohms, dependendo do padrão — que deve permanecer consistente ao longo de todo o caminho para evitar reflexões.

Por Que Pares Diferenciais São Essenciais Hoje

As taxas de dados aumentaram drasticamente em dispositivos modernos, de 480 Mbps no USB 2.0 a 20 Gbps por canal no PCIe 5.0. A transmissão single-ended enfrenta dificuldades com ruído e distorção nessas velocidades, levando a erros de bit. Pares diferenciais toleram comprimentos maiores de trilho e ambientes mais hostis, emitindo menos EMI. Tornaram-se padrão em eletrônicos de consumo, infotenimento automotivo e centros de dados, onde a integridade do sinal impacta diretamente o desempenho.

Principais Vantagens e Padrões Comuns para Pares Diferenciais

Benefícios em Relação à Transmissão Single-Ended

Pares diferenciais oferecem várias vantagens práticas. Fornecem excelente rejeição de modo comum, frequentemente 20–40 dB melhor que linhas single-ended, reduzindo suscetibilidade a ruído de terra e crosstalk. Emissões de EMI caem porque as correntes opostas cancelam campos magnéticos. Correntes de retorno permanecem confinadas entre o par e seu plano de referência, minimizando a área do loop. Em ambientes ruidosos como sistemas automotivos ou industriais, esses benefícios se traduzem em taxas de erro de bit menores e links mais robustos.

Padrões Populares e Requisitos Típicos de Impedância

A maioria das interfaces de alta velocidade especifica pares diferenciais com tolerâncias de impedância rígidas. Exemplos comuns incluem:

| Padrão | Impedância Diferencial Típica | Exemplo de Taxa de Dados | Observações |

| USB 2.0/3.0 | 90 Ω ±15% | 480 Mbps / 5 Gbps | Full-speed e SuperSpeed |

| HDMI 1.4/2.0 | 100 Ω ±10% | Até 18 Gbps | Pares TMDS |

| PCIe 3.0/4.0 | 100 Ω ±10% | 8–16 GT/s por canal | Alta tolerância a reflexões |

| Ethernet 1000BASE-T | 100 Ω ±10% | 1 Gbps | Emulação de par trançado na PCB |

Tabela 1: Padrões comuns de pares diferenciais e alvos de impedância.

Esses valores vêm de especificações de interface e exigem materiais dielétricos controlados e geometria de trilho durante a fabricação.

Regras Essenciais de Design para Pares Diferenciais Confiáveis

Controle de Impedância, Largura, Espaçamento e Correspondência de Comprimento

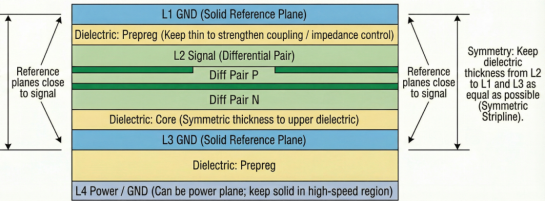

A impedância diferencial é calculada usando largura do trilho (W), espaçamento (S), altura ao plano de referência (H) e constante dielétrica (Er). Para um par típico de 100 Ω em FR-4, larguras de 4–6 mil com espaçamento de 5–8 mil e espessura de prepreg de 4–6 mil funcionam bem. Solucionadores de campo como Saturn PCB Toolkit ou calculadoras integradas em Altium/KiCad fornecem valores precisos com base no stackup. Variações em ataque químico ou dielétrico podem deslocar a impedância em 5–10%, então especifique tolerâncias nas notas de fabricação. Limite de correspondência de comprimento mantém distorção intra-par em 5–15 ps (dependendo do tempo de subida) — use padrões em sanfona ou dente de serra no trilho mais longo, mantendo amplitude baixa (<3x largura) para evitar indutância ou capacitância adicionais.

Planos de Referência, Caminhos de Retorno e Seleção de Camada

Um plano de referência contínuo (de preferência terra) imediatamente adjacente ao par é essencial para impedância estável e retorno de baixa indutância. Dividir planos força correntes de retorno a desvios, criando ruído de modo comum. Em projetos multicamada, prefira camadas internas para blindagem contra interferência externa, mas garanta que o stackup seja simétrico para controlar deformação durante laminação. Para placas com alta contagem de camadas, alterne camadas de sinal e plano para fornecer múltiplas referências. Vias de costura a cada 5–10 mm ao redor do perímetro do par ligam planos entre camadas.

Técnicas Avançadas de Roteamento e Práticas de Integridade de Sinal

Estratégias de Acoplamento, Tratamento de Vias e Redução de Crosstalk

Acoplamento rígido (S ≈ W) maximiza rejeição de modo comum, mas reduz impedância; acoplamento frouxo aumenta impedância para facilitar correspondência. Routeie pares com espaçamento constante e evite curvas abruptas — use ângulos de 45 graus ou arcos com raio >3x largura. Para vias, minimize stubs com back-drilling ou vias cegas/enterradas; coloque vias do par simetricamente e circunde com vias de terra (4–6 por par) para manter blindagem. Mantenha pares pelo menos 5H (altura ao plano) de distância de agressores para limitar crosstalk de extremidade distante abaixo de -40 dB

Ferramentas de Simulação e Considerações de Fabricação

HyperLynx ou SIwave para simulação pré e pós-layout revelam fechamento de olho ou reflexões cedo. Teste TDR verifica continuidade de impedância. Fatores de fabricação como rugosidade de cobre (folha de baixo perfil preferida), espessura de máscara de solda e uniformidade de ataque químico afetam perda e distorção. Processos controlados atingem precisão de impedância de ±8–10%, com cupons de teste em painéis para verificação. DFM regras incluem evitar armadilhas de ácido em espaçamentos apertados e garantir folga mínima broca-cobre para plaqueamento confiável.

Desafios Comuns no Design de Pares Diferenciais e Como Superá-los

Descontinuidades de Impedância, Distorção e Problemas de EMI

Curvas, conectores ou mudanças de camada criam quedas de impedância, causando reflexões que degradam aberturas de olho. Distorção intra-par excessiva converte diferencial em modo comum, aumentando EMI. Soluções incluem taperes graduais em transições, tolerância rígida de comprimento (<0,1 mm para >5 Gbps) e blindagem com áreas de terra ou vias.

Papel da Fabricação Profissional na Resolução de Tolerâncias

Variação de ataque e inconsistência dielétrica podem deslocar impedância em 10–15%. Fabricantes profissionais usam imagem direta a laser para padronização precisa, fluxo controlado de prepreg e teste de cupom de impedância para manter precisão de ±5–10%. Eles também otimizam stackup para materiais de baixa perda e fornecem feedback DFM precoce sobre estruturas de via ou viabilidade de espaçamento.

Conclusão

Pares diferenciais são críticos quando taxas de dados excedem 1 Gbps, margens de ruído apertam ou conformidade EMI é necessária — comum em interfaces modernas como USB-C, PCIe e vídeo de alta resolução. Implementação adequada garante olhos abertos, BER baixo e aprovação em certificações.

Para resultados confiáveis, parceire com um fabricante experiado em placas de alta velocidade. A JLCPCB oferece controle preciso de impedância (±10% padrão, mais rígido sob solicitação), suporte multicamada e HDI para roteamento denso, e prototipagem rápida para validar integridade de sinal cedo. Sua calculadora online e verificações DFM ajudam a refinar parâmetros de par diferencial antes da produção. Faça upload de seu projeto em jlcpcb.com para orçamento instantâneo e fabricação que atenda a exigentes requisitos de alta velocidade.

FAQ: Perguntas Comuns Sobre Pares Diferenciais

P1: Qual é a principal diferença entre transmissão diferencial e single-ended?

R: Diferencial usa dois trilhos complementares para cancelar ruído de modo comum, oferecendo melhor imunidade (20–40 dB) e menor EMI que single-ended, que depende de um único trilho e referência de terra.

P2: Quão rígida deve ser a correspondência de comprimento para pares diferenciais?

R: Mantenha distorção intra-par abaixo de 5–15 ps (ou <0,1 mm para sinais >5 Gbps) para prevenir erros de temporização e conversão de modo — use roteamento serpente no trilho mais longo.

P3: Por que um plano de referência sólido é crítico para pares diferenciais?

R: Garante impedância consistente, caminhos de retorno de baixa indutância e blindagem; separações de plano forçam desvios de corrente, criando ruído e descontinuidades.

P4: Posso rotear pares diferenciais em camadas externas?

R: Possível, mas não ideal — camadas internas oferecem melhor blindagem e estabilidade de impedância; camadas externas aumentam suscetibilidade a ruído externo e exigem guarda extra.

Saber mais

Pares Diferenciais em PCBs: Melhores Práticas para Roteamento, Controle de Impedância e Integridade do Sinal

Projetos digitais de alta velocidade dependem cada vez mais de pares diferenciais para transmitir dados de forma confiável em taxas de vários Gbps a dezenas de Gbps. Esses trilhos emparelhados transportam sinais de magnitude igual, mas polaridade oposta, permitindo que os receptores rejeitem ruído de modo comum enquanto preservam o sinal diferencial. Engenheiros usam pares diferenciais para interfaces como USB, HDMI, PCIe e Ethernet porque oferecem imunidade superior ao ruído e EMI reduzida em compara......

Controlo de Impedância em PCB: Garantindo a Integridade do Sinal em Circuitos de Alta Frequência

A impedância mede a oposição de um circuito elétrico quando uma corrente alternada é aplicada a ele. É a combinação da capacitância e da indução de um circuito elétrico em alta frequência. A impedância é medida em Ohms, semelhante à resistência. Se as impedâncias forem diferentes, ocorrem reflexos e atenuação que deterioram o sinal. Para circuitos analógicos ou digitais de alta frequência, é essencial proteger os sinais que se propagam na PCB contra danos. Na verdade, sinais acima de 100 MHz são impac......